Advanced Series in Electrical and Computer Engineering – vol. 13

### Chue San YOO

8

# SEMICONDUCTOR MANUFACTURING TECHNOLOGY

VU

World Scientific

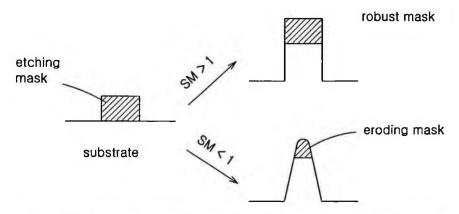

### SEMICONDUCTOR MANUFACTURING TECHNOLOGY

#### ADVANCED SERIES IN ELECTRICAL AND COMPUTER ENGINEERING

Editor: W. K. Chen (University of Illinois, Chicago, USA)

| Published: |                                                                                                                               |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Vol. 1:    | Broadband Matching: Theory and Implementations (Second Edition) by W. K. Chen                                                 |  |  |  |

| Vol. 2:    | Active Network Analysis<br>by W. K. Chen                                                                                      |  |  |  |

| Vol. 3:    | Linear Networks and Systems: Algorithms and Computer-Aided<br>Implementations (Second Edition) (Two Volumes)<br>by W. K. Chen |  |  |  |

| Vol. 4:    | Introduction to Engineering Electromagnetic Fields by K. Umashankar                                                           |  |  |  |

| Vol. 5:    | Graph Theory and its Engineering Applications by W. K. Chen                                                                   |  |  |  |

| Vol. 6:    | Introductory Signal Processing<br>by R. Priemer                                                                               |  |  |  |

| Vol. 7:    | Diagnostic Measurements in LSI/VLSI Integrated Circuits<br>Production<br>by A. Jakubowski, W. Marciniak and H. Przewlocki     |  |  |  |

| Vol. 8:    | An Introduction to Control Systems (Second Edition) by K. Warwick                                                             |  |  |  |

| Vol. 9:    | Orthogonal Functions in Systems and Control by K. B. Datta and B. M. Mohan                                                    |  |  |  |

| Vol. 10:   | Introduction to High Power Pulse Technology by S. T. Pai and Q. Zhang                                                         |  |  |  |

| Vol. 11:   | Systems and Control: An Introduction to Linear, Sampled and Nonlinear Systems<br>by <i>T Dougherty</i>                        |  |  |  |

| Vol. 12:   | Protocol Conformance Testing Using Unique Input/Output Sequences by X. Sun, C. Feng, Y. Shen and F. Lombardi                  |  |  |  |

| Vol. 13:   | Semiconductor Manufacturing Technology by C. S. Yoo                                                                           |  |  |  |

Advanced Series in Electrical and Computer Engineering - Vol. 13

### Chue San YOO

Former Associate Professor at Tamkang University ar National Tsing Hua University, Taiwan

## SEMICONDUCTOR MANUFACTURING TECHNOLOGY

NEW JERSEY - LONDON - SINGAPORE - BEIJING - SHANGHAI - HONG KONG - TAIPEI - CHENNAL

#### Published by

World Scientific Publishing Co. Pte. Ltd.

5 Toh Tuck Link, Singapore 596224

USA office: 27 Warren Street, Suite 401-402, Hackensack, NJ 07601

UK office: 57 Shelton Street, Covent Garden, London WC2H 9HE

British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library.

#### SEMICONDUCTOR MANUFACTURING TECHNOLOGY Advanced Series in Electrical and Computer Engineering — Vol. 13

Copyright © 2008 by World Scientific Publishing Co. Pte. Ltd.

All rights reserved. This book, or parts thereof, may not be reproduced in any form or by any means, electronic or mechanical, including photocopying, recording or any information storage and retrieval system now known or to be invented, without written permission from the Publisher.

For photocopying of material in this volume, please pay a copying fee through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA. In this case permission to photocopy is not required from the publisher.

ISBN-13 978-981-256-823-6 ISBN-10 981-256-823-9

Printed in Singapore by World Scientific Printers

#### Preface

Over the last 20 years, I have been intensively involved in semiconductor process technology research, development, and manufacturing. Alongside my professional career, I have also enjoyed teaching semiconductor processing at Tamkang and Chinghwa universities as an adjunct professor. The contents of this book have largely evolved from the handouts that I prepared over the years for these courses. I also revised the course material for training junior engineers at various semiconductor companies. My experience indicates that it is relatively difficult for people who first embrace the semiconductor world to comprehend the essence of semiconductor processing technology. This is largely due to the fact that most people have a single engineering discipline in schools, while semiconductor processing is interdisciplinary in nature. It even takes a person with an engineering degree a few years before he or she can gain a good grasp of the overall semiconductor processing technology.

This book aims to provide readers with an easy-to-understand view of semiconductor industry, technology, and manufacturing. The first two chapters provide an overview of the industry. This includes an introduction to semiconductor processing and what the industry is focusing on. In addition, the integrated manufacturing flow, from raw material to device passivation, is explained, and each involved process module is defined. It also explains what ICs are and what they consist of. The following chapters further elaborate each individual process module technology. By and large, the sequence of the process module introduction follows typical manufacturing flows. The

manufacturing processes are divided into two parts: the front-end and back-end processes. The former includes oxidation, gas kinetics, plasma physics, CVD, plasma CVD and etching, photolithography, mask making, and doping technology. The pattern generation or mask making is included since it is relatively unfamiliar to those who work in wafer processing. Furthermore, it is widely believed that the photomask technology has to be closely integrated into wafer processing to ensure wafer production success as technologies migrate beyond 0.13  $\mu$ m. The back-end process introduction, beginning with contact formation, primarily focuses on metallization and planarization and their technology evolution. Various silicide formation processes are also included in the metallization due to its inevitable role in advanced semiconductor manufacturing. Following the conventional back-end technology discussion, copper and low dielectric constant materials are also introduced as they are widely used in prevailing nanometer device manufacturing.

While most text is self-explanatory, some mathematics modeling is included occasionally to better explain the theories. Those who are in an undergraduate program or who do not have enough time to check into the mathematics can skip the modeling sessions and still gain insight into semiconductor manufacturing principles.

#### Acknowledgments

I am grateful to my late father, Ching mu Yoo, who gave me an unforgettable childhood. I would also like to thank my wife for her support over the past several years, when I was writing this book. To my 10-year-old son, Gordon. I like to tell you I am so proud of your drawing on the cover page. Thank you so much. I am indebted to the engineers I have taught in various semiconductor companies and all the students I have taught in the past 15 years at Tamkang University and Chinghwa University. They have helped greatly in shaping the contents of this book.

#### Contents

| PR | EFAC | )E                                            | v   |

|----|------|-----------------------------------------------|-----|

| AC | KNO  | WLEDGMENTS                                    | vii |

| 1. | OVE  | CRVIEW                                        | 1   |

|    | 1.1. | Classification of Materials                   | 1   |

|    | 1.2. | Evolution of Integrated Circuit (IC) Industry | 4   |

|    | 1.3. | From Design to Chips                          | 8   |

|    | 1.4. | The Wafer Substrate Manufacturing Flow        | 12  |

|    | 1.5. | Wafer Processing Flow                         | 19  |

|    | 1.6. | What Is the Semiconductor Industry Trying     |     |

|    |      | to Achieve?                                   | 26  |

|    | 1.7. | The Never-Ending Effort — Yield Improvement   | 31  |

| 2. | BUI  | LDING BLOCKS FOR INTEGRATED CIRCUITS          | 38  |

|    | 2.1. | Fundamental Semiconductor Concepts            | 38  |

|    | 2.2. |                                               | 47  |

|    | 2.3. | The $pn$ Junctions $\ldots$                   | 50  |

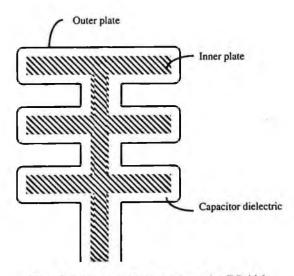

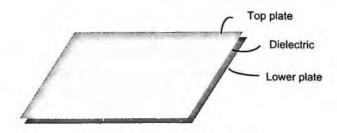

|    | 2.4. | Capacitors                                    | 52  |

|    | 2.5. | The MOS Transistor                            | 55  |

|    | 2.6. | Integrated Circuits                           | 58  |

| 3. | THE  | CRMAL OXIDATION                               | 63  |

|    | 3.1. | Introduction                                  | 63  |

|    | 3.2. | Oxidation Mechanism and Modeling          | 68    |

|----|------|-------------------------------------------|-------|

|    | 3.3. | Isolation Technology                      | 78    |

|    | 3.4. | Gate Oxide                                | . 86  |

|    | 3.5. | Cleaning before Thermal Oxidation         | . 91  |

| 4. | GAS  | KINETICS AND PLASMA PHYSICS               | 97    |

|    | 4.1. | Gas Kinetics and Ideal Gases              | . 97  |

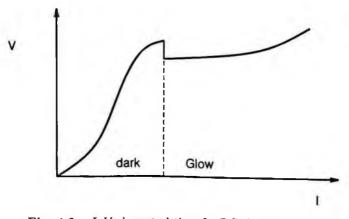

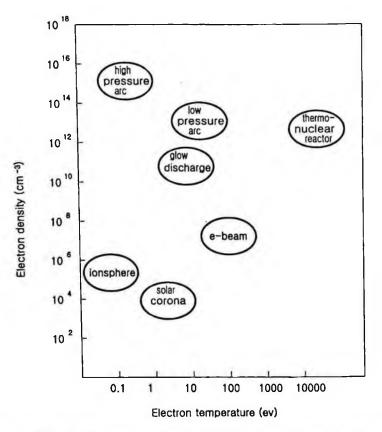

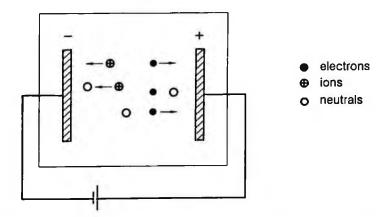

|    | 4.2. | What Is Plasma? How Is It Formed?         | 104   |

|    | 4.3. | Introduction to Plasma Physics            | . 110 |

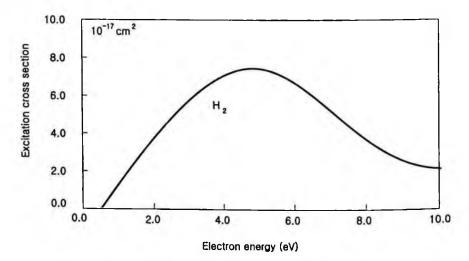

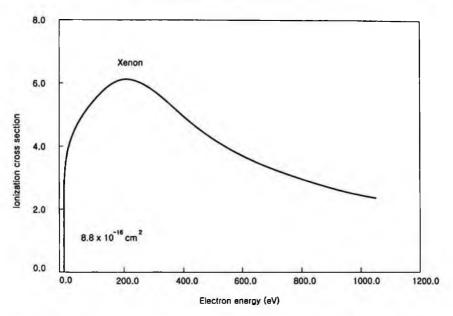

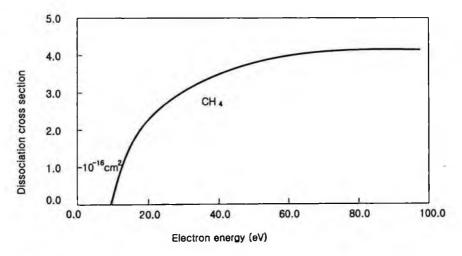

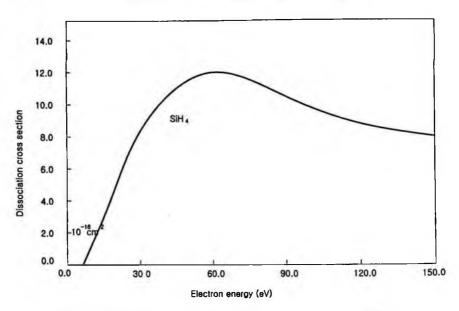

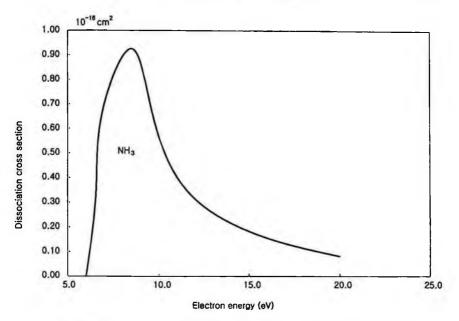

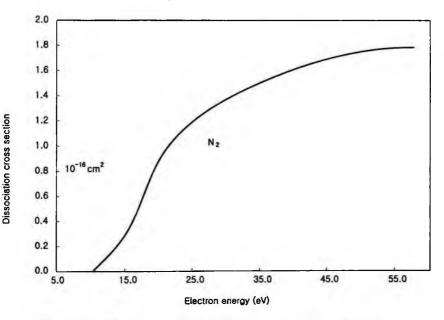

|    | 4.4. | Electron Impact Phenomena                 | 114   |

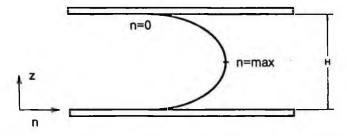

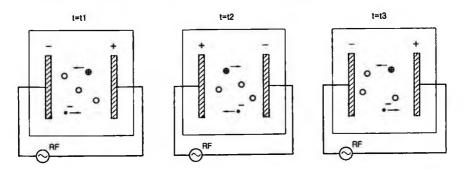

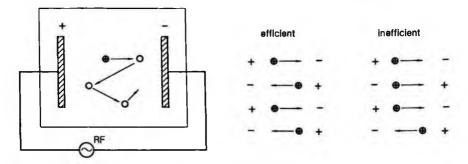

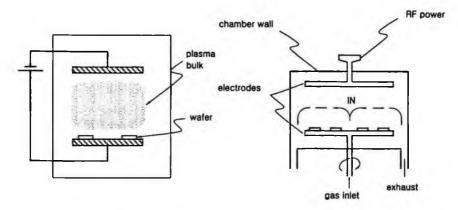

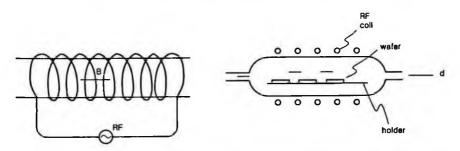

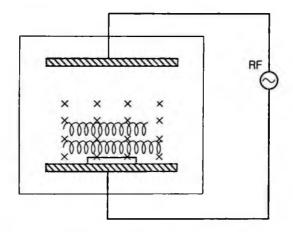

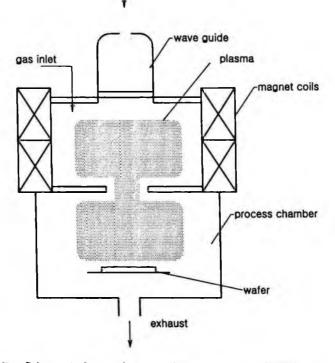

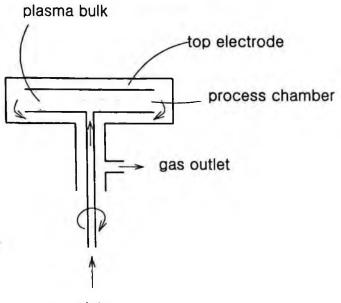

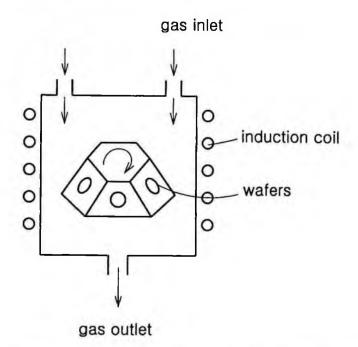

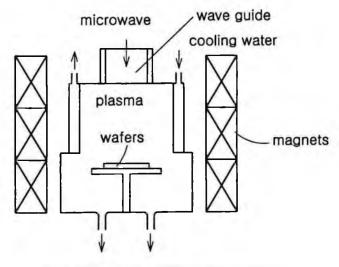

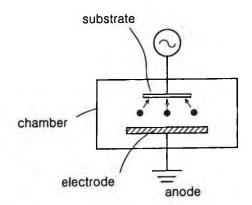

|    | 4.5. | Fundamental Plasma Reactor Configurations | 120   |

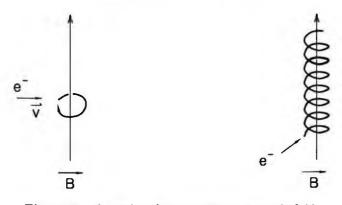

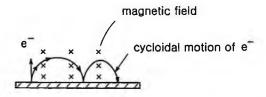

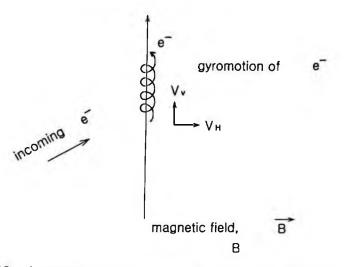

|    | 4.6. | Magnetic Field Confinement                | . 124 |

| 5. | CHE  | MICAL VAPOR DEPOSITION                    | 128   |

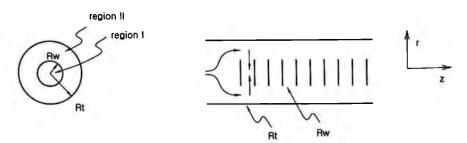

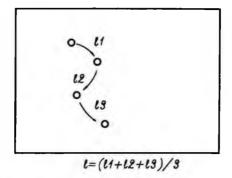

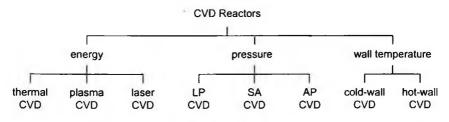

|    | 5.1. | Classification of CVD Reactors and Films  | . 128 |

|    | 5.2. | CVD Reactor Design Concepts               |       |

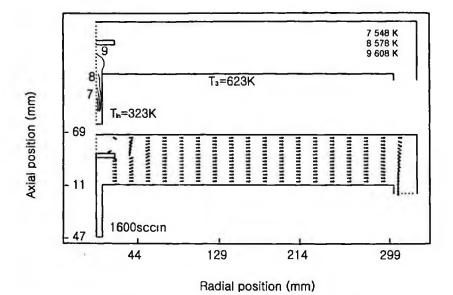

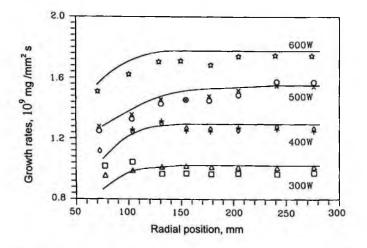

|    | 5.3. | CVD Reactor Modeling                      | 136   |

|    | 5.4. | Characterization of Thin Films            | . 146 |

|    | 5.5. | Applications of CVD Films                 | 153   |

| 6. | PLA  | SMA-ENHANCED CHEMICAL VAPOR               |       |

|    | DEP  | OSITION AND ETCHING                       | 168   |

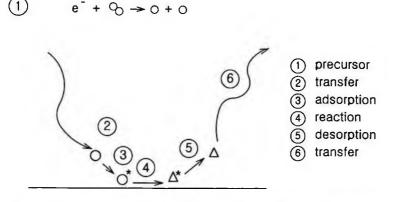

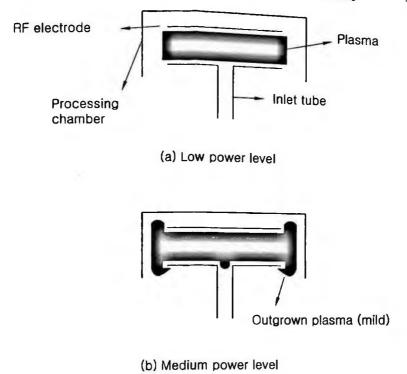

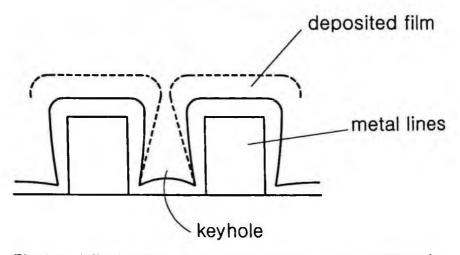

|    | 6.1. | The Plasma Reaction Pathways and          |       |

|    |      | System Variables                          | . 168 |

|    | 6.2. | Introduction to PECVD and Film            |       |

|    |      | Characterization                          | . 174 |

|    | 6.3. | Applications of PECVD Films               | . 178 |

|    | 6.4. | Introduction to Plasma Etching            | . 185 |

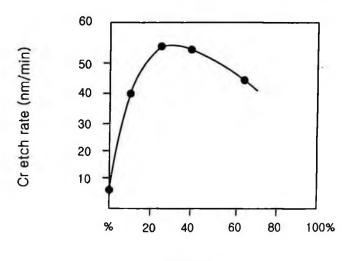

|    | 6.5. | Applications of Plasma Etching            | . 190 |

|    | 6.6. | Plasma-Enhanced CVD and Etching Reactor   |       |

|    |      | Modeling                                  | 205   |

| 7. | PAT  | TERN TRANSFER: PHOTOLITHOGRAPHY           | 212   |

|    | 7.1. | Introduction                              | . 212 |

|    | 7.2. |                                           |       |

| Contents |

|----------|

|----------|

|     | <ol> <li>7.3.</li> <li>7.4.</li> <li>7.5.</li> <li>7.6.</li> </ol>               | Resist Chemistry               | 233<br>250        |

|-----|----------------------------------------------------------------------------------|--------------------------------|-------------------|

| 8.  | PAT                                                                              | TERN GENERATION                | 260               |

|     | 8.1.<br>8.2.<br>8.3.<br>8.4.                                                     | Introduction                   | 267<br>277        |

| 9.  | DOP                                                                              | ING TECHNOLOGY                 | 304               |

|     | <ol> <li>9.1.</li> <li>9.2.</li> <li>9.3.</li> <li>9.4.</li> <li>9.5.</li> </ol> | Introduction                   | 310<br>317<br>327 |

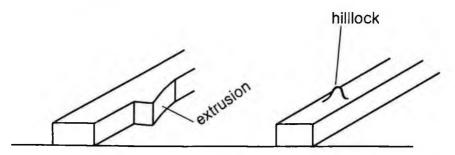

| 10. | MET                                                                              | TALLIZATION AND SILICIDATION   | 338               |

|     | 10.2.<br>10.3.<br>10.4.                                                          | Introduction                   | 346<br>349<br>357 |

| 11. | PLA                                                                              | NARIZATION AND CMP TECHNOLOGY  | 378               |

|     | 11.2.<br>11.3.<br>11.4.                                                          | Introduction                   | 382<br>389<br>392 |

|     | 11.6.                                                                            | Polishing and Its Applications | 398<br>409        |

xi

Semiconductor Manufacturing Technology

| 12. | COPPER AND LOW-k                                                              | 411 |

|-----|-------------------------------------------------------------------------------|-----|

|     | 12.1. Back-End Processes                                                      |     |

|     | 12.2. Cu Wiring                                                               | 415 |

|     | 12.3. Low-k Dielectrics $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 431 |

|     | 12.4. Integration of Copper and Low- $k$ Materials                            | 435 |

| GL  | OSSARY                                                                        | 440 |

| RE  | FERENCES                                                                      | 453 |

| INI | DEX                                                                           | 465 |

#### Chapter 1

#### **OVERVIEW**

This chapter provides an introduction to the semiconductor industry. It begins with the classification of solids in terms of resistivity and introduces the semiconductor industry's evolution from its early stage to the prevailing planar technology. It then illustrates each of the six major chip manufacturing stages: design, mask making, wafer substrate making, wafer processing, back-end service, and qualification. The substrate and wafer processes are elaborated with schematic process flows. The last two sections are dedicated to explaining what the semiconductor industry is focusing on and where it is devoting its efforts.

#### 1.1. Classification of Materials

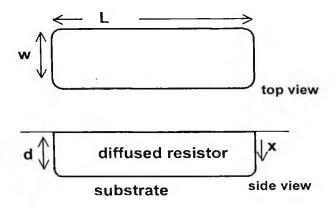

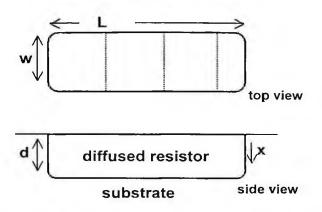

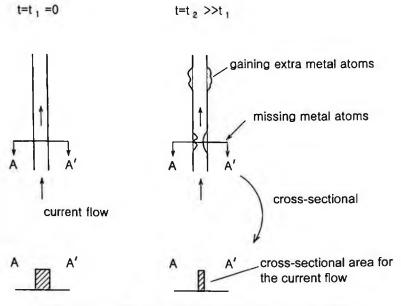

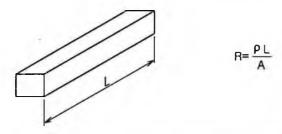

A semiconductor device is made up of a wide variety of materials, ranging from insulators, such as silicon oxides or silicon nitrides, to excellent conductors, such as aluminum and copper. Most important, it is based on the semiconductor. What is a semiconductor? This can be explained from a resistivity viewpoint. The resistance of a material is a function of its geometry:

$$R=\rho\frac{L}{A}\,,$$

where R is the resistance of the material, L is the length of the material, A is the cross-sectional area perpendicular to the current flow, and  $\rho$  is the resistivity of the material, which is a physical property of the material.

| Materials                                         | Resistivity ( $\Omega$ -cm) |

|---------------------------------------------------|-----------------------------|

| SiO <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub> | > 10 <sup>5</sup>           |

| Si                                                | $5 \times 10^4$             |

| Ge                                                | 50                          |

| Heavily doped Si                                  | $10^{-4}$                   |

| Cu                                                | 10 <sup>-6</sup>            |

Table 1.1.Resistivities of materialsused in semiconductor manufacturing.

Conductors have a resistivity of less than 0.01 Ohm-cm, while insulators have a resistivity of greater than 100 000 Ohm-cm. Materials with resistivities ranging between those of the conductors and insulators are called semiconductors. Table 1.1 shows the resistivities of different materials that are often used in semiconductor manufacturing. Silicon oxide and silicon nitride are good insulators that are often used for isolation between conductors and passivation layers. Silicon and germanium are typical wafer substrates on which devices are made. Copper, on the other hand, is used for interconnects.

Resistivities of solid materials are related to the way the atoms or molecules are bonded together. The intermolecular or interatomic forces characterize the solids, which are classified into four groups (molecular, ionic, covalent, and metallic). Table 1.2 shows the materials that are used in semiconductor manufacturing as well as their classifications.

The elements in columns II to VI in the periodic table are considered semiconductor materials. Table 1.3 shows the electronic configuration and some of the properties of each element in column IV. Silicon and germanium are elemental semiconductors, and each atom has four valence electrons. On the other hand, elements in columns II and VI, e.g., Zn and S, or columns III and V, e.g., Ga and As, can form compound semiconductors such as ZnS and GaAs. The common feature of the semiconductor materials is that each atom has effectively four valence electrons. When bonded to other atoms, they form covalent bonds. Germanium was the material of choice for major device fabrication in the early years of semiconductor production. It has lower resistivity than silicon. However, owing to its

|                                          | Molecular                                           | Ionic                  | Covalent         | Metallic        |

|------------------------------------------|-----------------------------------------------------|------------------------|------------------|-----------------|

| Units occupying<br>lattice sites         | Molecules                                           | Ions                   | Atoms            | Positive ions   |

| Interunit forces                         | van der Waals                                       | Electrostatic          | Shared electrons | Ions-electrons  |

| General<br>properties                    | Soft                                                | Hard                   | Very hard        | Varies          |

| Melting point                            | Low                                                 | High                   | Very high        | Varies          |

| Conductivity                             | Insulators                                          | Insulators             | Semiconductors   | Good conductors |

| Examples in<br>semiconductor<br>industry | N <sub>2</sub> , H <sub>2</sub> , CO <sub>2</sub> * | NaOH, HCI <sup>†</sup> | C, Si, Ge        | Al, Cu, W       |

Table 1.2. Bonding natures of solids and examples in semiconductor manufacturing.

\*N<sub>2</sub>, H<sub>2</sub>, CO<sub>2</sub>: when condensed to solid.

<sup>†</sup>NaOH, HCl: in water solution for wafers or masks cleaning process.

| Elements | Z  | Electronic configuration          | M.P.,°C | B.P.,°C | Ionization<br>potential, eV |

|----------|----|-----------------------------------|---------|---------|-----------------------------|

| С        | 6  | (2) $2S^22P^2$                    | 3500    | 4000    | 11.26                       |

| Si       | 14 | (2) $2S^22P^2$<br>(10) $3S^23P^2$ | 1400    | 2400    | 8.15                        |

| Ge       | 32 | $(28) 4S^2 4P^2$                  | 937     | 2800    | 8.13                        |

| Sn       | 50 | $(48) 5S^25P^2$                   | 232     | 2260    | 7.33                        |

| Pb       | 82 | $(78) 6S^2 6P^2$                  | 327     | 1700    | 7.42                        |

Table 1.3. Elements in column IV of the periodic table.

limited sources, it is much more expensive than silicon. Germanium is brittle and its oxide is soluble in water, which limits its applications in realizing planar processing technology. As semiconductor device production volume increased and its applications multiplied, germanium was soon replaced by silicon.

Silicon is the second richest element on earth, next to oxygen. Therefore it is relatively cheap and easy to access compared to other elements. The fact that silicon dioxides are not soluble in water gave rise to planar processing technology in 1959. By far, silicon is the most commonly used elemental material in the semiconductor industry. In addition, GaAs is the most commonly used compound semiconductor material. The biggest advantage of using GaAs is that the electron mobility of GaAs is ten times faster than that of silicon. One can imagine that a calculation task can be accomplished by GaAs devices a few times faster than by silicon devices. However, the manufacturing technology for GaAs has been lagging behind that of silicon. Until recent years, device manufacturing using GaAs has remained a small-scale production. One of the major limitations is the thermal budget. As processing temperature increases, arsenic (As) may outgas from the substrate material. Arsenic is extremely toxic in nature. Furthermore, as more arsenic atoms outgas from the substrate, the substrate becomes richer in Ga, and therefore it loses its intrinsic semiconducting characteristics.

#### 1.2. Evolution of Integrated Circuit (IC) Industry

The first half of the twentieth century can be considered the vacuum tube era. It was inspired by J. A. Fleming, who invented the vacuum tube diode in 1904 by using the Edison effect. The vacuum tube functioned as a valve, conducting current in only one direction. In 1906, Lee De Forest inserted a third electrode into the diode to obtain a triode, which amplified the input signals. After that, all electronic devices ranging from radios and TV sets to computers were made of vacuum tubes. However, the vacuum tubes were big, fragile, and power consuming. Electronic appliances that were made up of vacuum tubes needed to be interrupted after being used for a period of time to avoid overheating. The world's first successful computer --The University of Pennsylvania's ENIAC - comprised some 18000 vacuum tubes. The footprint of the ENIAC was big enough to fill up a huge room. Whenever it shuts down due to overheating, the maintenance engineers often needed to search for the burnt-out tube out of tens of thousands of tubes. Complicated systems with vacuum tubes were very difficult to maintain.

With the demonstration of transistor functions accomplished by Walter H. Brattain, John Bardeen, and William Shockley in 1947 and the invention of the semiconductor integrated circuit (IC) by Jack Kilby in 1958, the use of vacuum tubes began to be replaced rapidly by devices made of semiconductor materials. Today, the applications of semiconductor devices, ranging from everyday appliances

| Milestones                            | Inventors                        |  |

|---------------------------------------|----------------------------------|--|

| Vacuum tube diode                     | J. A. Fleming, 1904              |  |

| Vacuum tube triode                    | Lee De Forest, 1906              |  |

| Vacuum tube computer, ENIAC           | University of Pennsylvania, 1946 |  |

| Semiconductor transistor              | William Shockly et al., 1947     |  |

| Integrated circuit (IC)               | Jack Kilby, 1958                 |  |

| Silicon planar technology             | J. A. Hoerni, 1959               |  |

| Microprocessor, >1 K transistors      | Intel 4004, 1971                 |  |

| 1 Kb DRAM                             | Intel's 1103, 1970               |  |

| Microprocessor, $> 9.5$ M transistors | Intel's Pentium III, 1999        |  |

| Microprocessor, > 42 M transistors    | Intel's Pentium 4, 2000          |  |

Table 1.4. Milestones in electronic industry evolution.

to communication devices and computers, are much broader than those made of vacuum tubes. Table 1.4 shows the major milestones in the human electronic evolution. It is evident that the technology advanced with an astonishing speed. With the invention of integrated circuits and planar processing technology, people began to put a large number of devices on the same chip (or die). The number of devices per chip increases with advances in processing technology. Over the last 30 years, the packing density has increased almost 10 000 times. The level of integration has evolved from large-scale integration (LSI >  $10^3$  devices/chip) to very large scale integration (VLSI >  $10^5$  devices/chip) to today, with ultra large scale integration (ULSI >  $10^7$  devices/chip). Nonetheless, the technology still has a lot of room for improvement in terms of size, speed, and cost.

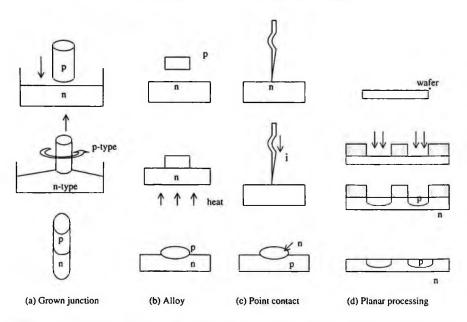

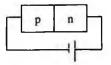

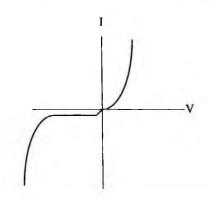

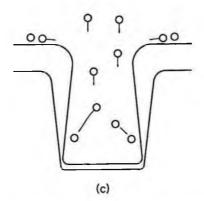

The high packing density is made possible by the silicon planar processing technology, which has evolved over the past generations. Using a diode manufacturing process as a vehicle, one can gain insight into the silicon processing technology evolution, as shown in Fig. 1.1. The grown junction method basically dips a *p*-type substrate into an *n*-type silicon melt. As the *p*-type substrate is pulled up, the *n*-type melt crystallizes next to the *p*-type substrate. Therefore a *p*-*n* junction is formed. The alloy junction, on the other hand, is formed by placing an *n*-type pellet onto a *p*-type substrate. As the temperature is raised above the silicon melting point and then cooled

Fig. 1.1. Junction formation approaches, illustrating the evolution of semiconductor processing technology.

down, an alloy junction can be formed. These two approaches result in junctions with large capacitances, owing to large junction areas.

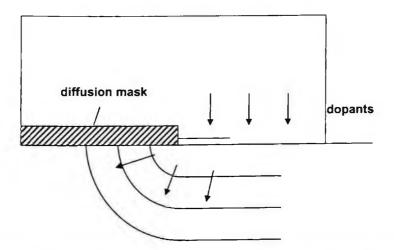

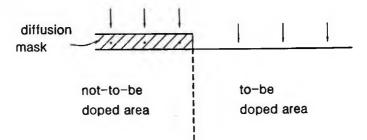

The point contact junction approach brings an *n*-type whisker in contact with a *p*-type substrate surface, and when a high current is passed through the whisker, the local heating brings about a small area p-n junction. Therefore a small capacitance junction diode can be obtained. The technologies mentioned earlier are either difficult to control or too difficult to mass produce. Silicon planar processing technology (described by J. A. Hoerni in 1960), which employs a silicon oxide mask to define the size of a diode, enables a huge number of devices to be made simultaneously on the same silicon wafer surface. Planar processing technology results in capacitors with different capacitances and excellent controllability. This is made possible by two unique features of silicon: (1) silicon can be oxidized to obtain silicon dioxide, which is a stable insulator, and (2) silicon and silicon dioxide have a good chemical durability during wafer cleaning. Overview

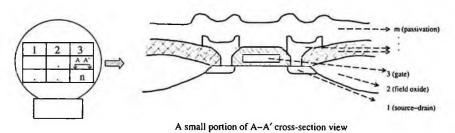

Fig. 1.2. A single silicon wafer contains n discrete dice. Each die is made of m layers of different materials defined by m layers of masks.

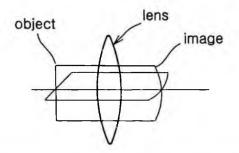

Prevailing silicon planar processing technology is far more complicated than it used to be. Figure 1.2 shows the cross-section of a simplified, single-layer metal circuit structure. It defines a device structure into *m* layers. Each layer corresponds to a photomask. The layers are made up of different materials and are manufactured layer by layer. The pattern within each layer is divided into n regions. Each region designates an individual chip or die. The planar technology enables device manufacturing to transform from a discrete to an integrated level. The combination of planar technology and integrated circuit design greatly accelerated the evolution of the semiconductor industry. As the technology advances, the mask number, m, increases to increase the packing density. One example of this is the use of multilayer metal to increase the level of integration. Meanwhile, the number of dice, n, can be increased to reduce the cost per die. This is accomplished by using a smaller geometry technology, assuming the chip function stays unchanged.

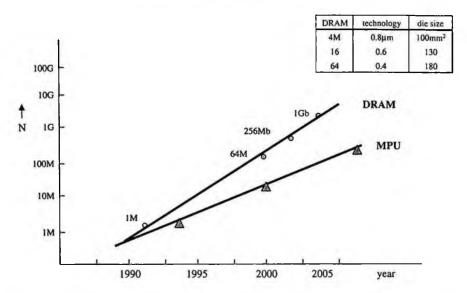

The silicon planar processing technology has been evolving since 1960. Today, hundreds of millions of transistors can be packed onto a tiny die. Figure 1.3 shows the volume production of 1 M DRAM during 1991, while the current technology is capable of producing 256 Mb DRAM. The 1-Gb DRAM is now in volume production. The level of integration is expected to increase a thousand fold by the year 2016. The memory size of 1 Gb DRAM corresponds to 64 000 sheets of newspaper. For the microprocessor, the level of integration is expected to increase ten-fold by the year 2010. With the prevailing semiconductor processing technology, the ENIAC computer could be

Fig. 1.3. As semiconductor technology shrinks, the number of transistors per die (either on DRAM or MPU) increases dramatically, but the die size increases disproportionately (N: the number of transistors per die).

shrunk onto a tiny chip smaller than  $1 \text{ mm}^2$ , and yet it will be even more powerful and will perform faster computing functions.

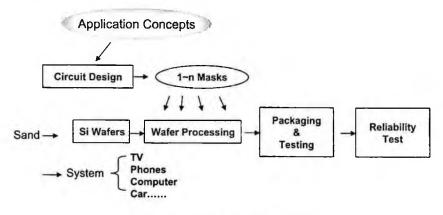

#### 1.3. From Design to Chips

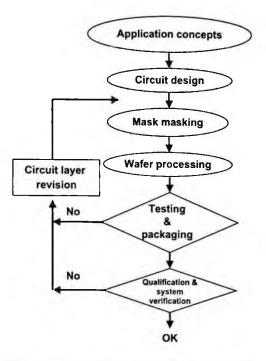

The process of manufacturing silicon chips begins with high-quality sand as a raw material and ends with the resulting silicon chips, which are used in end product such as PCs, TVs, or other electronic appliances. This entire process can be divided into six different stages, as illustrated in Fig. 1.4. These subprocesses are as follows: (1) circuit design; (2) mask making; (3) silicon substrate manufacturing; (4) wafer processing; (5) back-end services, including testing; and packaging; and (6) qualification. The circuit design defines a circuit that meets the specified functions, performance, and cost. A circuit design primarily includes two phases. One phase is the logical design, while the other phase is the physical layout design. The logical design determines the circuit structures needed to implement the prescribed

Fig. 1.4. From design to packaged chips.

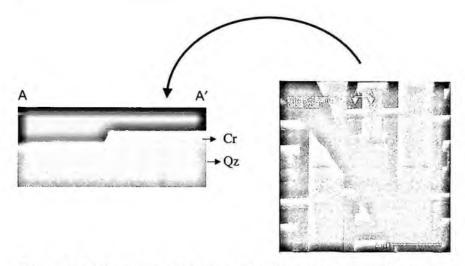

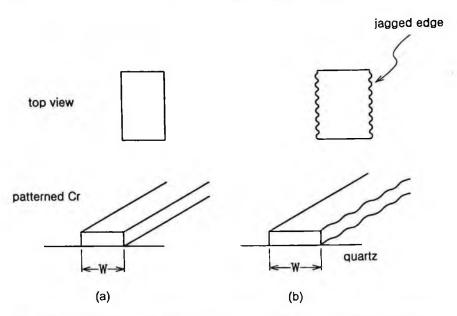

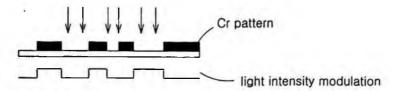

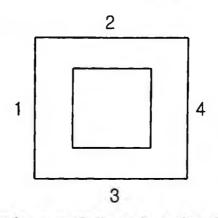

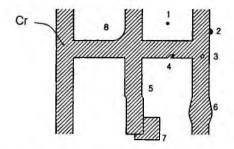

function. The physical layout design concerns the implementation of the circuit structure on the silicon substrate. In this phase, the circuit is separated into different levels, and each level is represented by a large number of polygons, as illustrated in Fig. 1.5. The output of the product circuit design is the physical layout pattern of a number of layers. A mask shop takes each layer's pattern information and generates the layout patterns on a mask, chrome patterns on quartz, as demonstrated in Fig. 1.6. A circuit or product generally consists of a number of masks, depending on the complexity of the product and wafer process technology. The masks must be used sequentially

Fig. 1.5. Examples of circuit patterns composed of polygons.

Fig. 1.6. Mask patterns with chrome on quartz and the cross-sectional view.

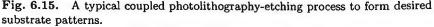

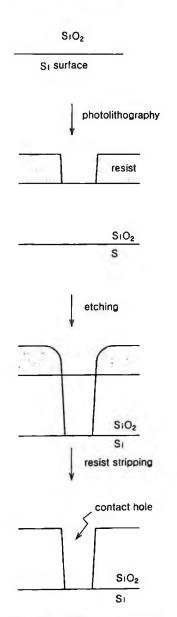

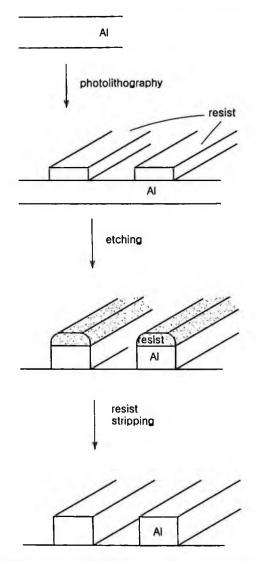

in the designated order to produce a functional product. Each mask is used in the wafer's photolithographic process step, followed by an etching for selective or local material removal for pattern delineation on wafers.

The circuit patterns are transferred from the masks to the wafer surface layer by layer, using the photolithographic process. The wafer substrate making and wafer processing will be discussed in detail in the following sections. The wafer processing is used to make a large number of transistors on a planar silicon surface, connecting them together to render a functional circuit. The wafers have to undergo electrical testing to determine whether the electrical functions comply with the original design requirements. If they do not meet the requirements, the circuit must be revised and retested until the function is optimized, as illustrated in Fig. 1.7. After the testing is completed, a product qualification procedure is required. The purpose of the product qualification is to ensure statistically that the manufactured chips are functioning properly under extreme environmental conditions for a certain lifetime. To accomplish this product qualification, each wafer is sawed into individual dice. It is then packaged and tested in various severe environmental and operational condition such

Fig. 1.7. Iterative procedure for circuit design.

| Table 1.5. | Product qualification | items and | stress condition | ons. |

|------------|-----------------------|-----------|------------------|------|

|------------|-----------------------|-----------|------------------|------|

| Items                                    | Stress condition                             |  |

|------------------------------------------|----------------------------------------------|--|

| (1) High-temperature operating life test | 125°C, 1000 h                                |  |

| (2) Temperature and humidity bias test   | 85°C, 85% RH, 1000 h                         |  |

| (3) Pressure cook test                   | 121°C, 2 atm, 100% RH, 200 h                 |  |

| (4) Temperature cycling (air to air)     | - 65°C 10 min to 50°C 10 min,<br>1000 cycles |  |

| (5) Thermal shocks test (liq. to liq.)   | - 65°C 5 min to 150°C 5 min,<br>200 cycles   |  |

as extreme humidity, temperatures, and operating voltages. Table 1.5 shows some typical product qualification items and their corresponding stress conditions. A functional chip design is not achieved unless the final qualification and system verification have been completed successfully.

#### 1.4. The Wafer Substrate Manufacturing Flow

To achieve a high yield in the wafer manufacturing process, it is essential for the process to begin on a high-quality single crystalline silicon substrate. The wafer substrate manufacturing process plays a critical role in this regard. To achieve this goal, high-quality sand (primarily silicon dioxide) is heated to above 1600°C to molten silicon and then reduced with carbon to form polycrystalline silicon:

$$SiO_2 + 2C \longrightarrow Si + 2CO_2$$

.

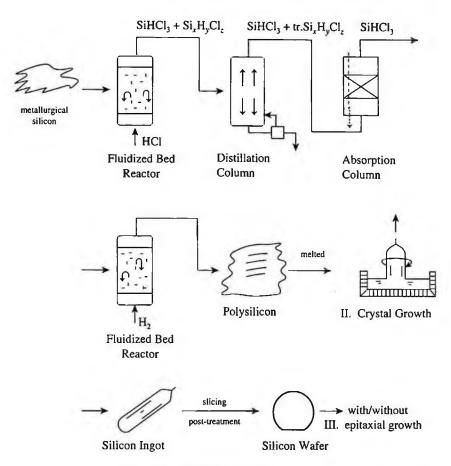

The polycrystalline silicon at this stage is a metallurgical-grade silicon that contains excessive impurities such as heavy metals, carbon, and oxygen in the range of several hundreds of parts per million. It is not qualified for making devices on its surface. Therefore further refining processes, as illustrated in Fig. 1.8, are required. The metallurgical-grade silicon is fed into a fluidized bed, where it reacts with HCl to produce various chlorosilanes such as monochlorosilane, dichlorosilane, and tricholorosilane (TCS):

$$Si + 3HCl \longrightarrow SiHCl_x + H_2$$

,

where x can be 1, 2, or 3.

These products are fed into a distillation column. The distillation is a mass separation process that takes advantage of the different boiling points of solvents in a solution. The lower boiling constituent TCS is obtained from the top of the column. It is then further purified using an absorption tower. The absorption is a mass separation process that relies on the fact that solutes can have different solubility levels in a solvent. The absorption tower and the solutes flow in opposite directions in the absorption tower. The resulting TCS is further reduced with hydrogen in another fluidized bed reactor to form electronic-grade polycrystalline silicon:

$$2SiHCl_3 + 2H_2 \longrightarrow 2Si + 6HCl$$

.

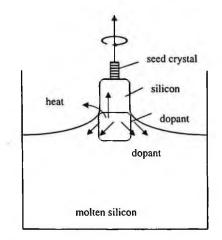

The newly obtained polycrystalline silicon meets the purity requirement of the electronic-grade silicon. It is then heated in a crucible, made of high-purity carbon, to a molten state for Czechralski crystal Overview

Fig. 1.8. Polysilicon refining process.

growth. A seed silicon crystal with a preferred crystal orientation is dipped into the surface of the molten silicon and pulled up, as illustrated in Fig. 1.9. Owing to the surface tension, some molten silicon is dragged out of the molten silicon surface. In the meantime, heat is transferred from this surface outward, resulting in crystallization. To maintain uniformity, the seed crystal is rotated while it is pulled up. The orientation of the grown silicon crystal follows that of the seed crystal. The seed crystal, together with the grown silicon, is pulled up very slowly, at a rate of several centimeters per day, allowing for heat transfer and to maintain the continuous silicon growth. In general,

Fig. 1.9. Silicon crystallizes onto the seed crystal.

the substrate is lightly doped. Dopants, such as boron, phosphine, or arsenic, can be added to the molten silicon to obtain an n-type or p-type substrate.

During the crystal growth process, there is intricate heat and mass transport around the solidification zone. The solidification process that occurs at the molten and solid interface releases latent heat. The released latent heat is proportional to the amount of solid formed and must be conducted away via the conduction along the solid bulk. As a result, the maximum pulling rate is proportional to the thermal conductivity of the silicon bulk and the temperature gradient along the pulling-up direction. If the pull-up rate is faster than the growth rate, the crystal growth is discontinued. However, if the reverse situation is observed, the grown solid will remelt. This can result in defects and impurity striations. Furthermore, the maximum pulling rate is inversely proportional to the square root of the grown ingot radius. It is easy to comprehend that a larger ingot radius would take a longer time for the latent heat to transfer out of the solidification zone.

Mass transfer is primarily concerned with the dopant redistribution at the solid-liquid interface. Consistent dopant concentration along the ingot growing direction is very critical as it is related to

#### Overview

device characteristics on each wafer. Theoretically, to obtain a uniform dopant concentration along the grown ingot length, it is essential to have a large bath of molten silicon such that the weight of the grown ingot is small compared to the bath.

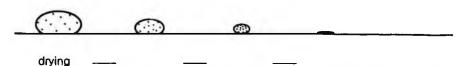

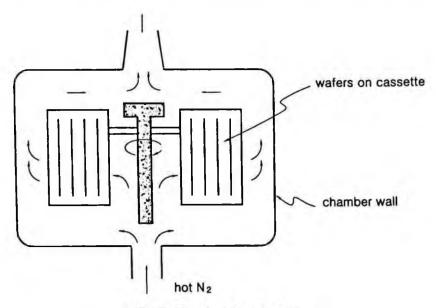

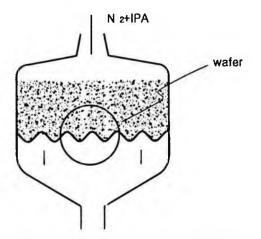

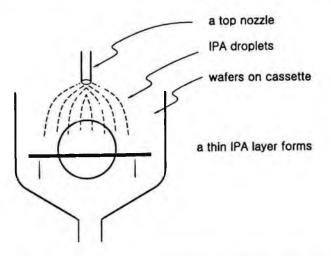

For device manufacturing, a critical index of the silicon ingot is the crystal orientation. Flats or notches are made on the ingot to indicate the crystal orientation and for wafer alignment in subsequent process steps. The ingot is then ground to the desired diameter. After the desired diameter has been obtained, the ingot is sliced with a diamond saw into thin disks, called wafers. The slicing process is followed by a lapping step, in which wafers are mechanically lapped with counter rotating lapping machines, along with aluminum oxide slurry. The wafer then goes through a chemical-mechanical polishing process, in which the silicon surface material is removed both chemically and mechanically using an alkaline silica solution. This step is intended to obtain an extremely flat and smooth silicon surface. The final step of the substrate manufacturing process is wafer cleaning and drying. Wafers are often cleaned with a three-step cleaning procedure, starting with SC1 solution, ammonia, and hydrogen peroxide for removing organic surface contaminants and particles. Hydrofluoric acid is used to remove the native oxide and metal impurities. The cleaning step ends with SC2 solution, HCl, and H<sub>2</sub>O<sub>2</sub> for a thin layer of super-clean native oxide formation. The state of the art wafer substrate size is 12 inches for production. However, eight- and six-inch wafer sizes are also being used for some production lines. The evolution trend for the size of the wafer substrate is to push for ever increasing wafer size. The reason for this trend is that the larger the wafer size, the more devices can be made simultaneously on the same wafer substrate. As a result, the manufacturing cost per die can be significantly reduced if the same level of wafer yield is achieved.

#### Example 1.1.

Assume that the housing facility and equipment required for the fabrication of a 12-inch wafer are twice more expensive than those required for the fabrication of an eight-inch wafer. If the eight-inch

wafer fabrication is running at 80% wafer yield, what is the minimum 12-inch wafer yield to make the 12-inch line economically worthwhile?

To make the 12-inch line economically worthwhile, to the firstorder approximation, one must have twice as many good dies on the 12-inch wafer compared to the eight-inch wafer:

$A8 \times 80\% \times 2 = A12 \times Y.$

Then,  $Y = A8 \times 80\% \times 2/A12$ . Therefore Y = 71%.

In addition to the yield, there are other advantages with large wafer sizes. First, with a large wafer size, the cross-over wafer yield is lower. Therefore there is a higher potential to improve the yield. In addition, with the same real estate area, the 12-inch fabrication revenue can be doubled. Furthermore, the productivity or sales per head count can be significantly increased.

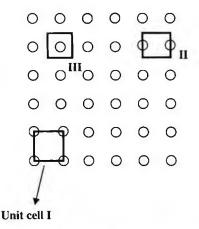

The silicon crystal orientation is of great importance in affecting the device performance. In a crystal, atoms have a unique arrangement. A unit cell is the smallest repeating unit in a crystal. In other words, by stacking up the unit cell, one can obtain the crystal structure. As shown in Fig. 1.10, more than one method of choosing a unit cell exists for a crystal. The unit cell constant refers to the

Fig. 1.10. More than one ways of choosing a unit cell.

16

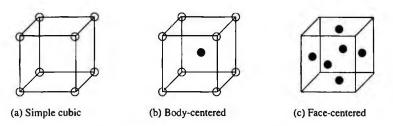

Fig. 1.11. Simple cubic crystals.

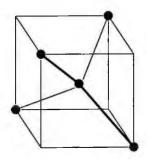

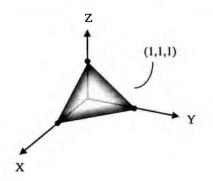

length of one side of the unit cell. If the unit cell constants happen to be the same along the three crystallography axes, the crystal is termed cubic. Figure 1.11 illustrates various crystal structures in the cubic class. Silicon crystal structure fits within the diamond structure, which is formed by two intercepting face-centered-cubic crystals. Each atom is surrounded by four other atoms through covalent bonds, forming a tetrahedron, as illustrated in Fig. 1.12. The Miller index is an index used to identify the crystal orientations or planes. The Miller index of a plane can be obtained using the following steps:

- (a) Take the intercepts of the plane with each axis, in terms of multiples of the unit cell length.

- (b) Take the reciprocal of each intercept.

- (c) Clear the fractional numbers.

Fig. 1.12. The silicon tetrahedron in a diamond lattice cell an david up

inv. No 25107

Fig. 1.13. The (111) plan.

Fig. 1.14. The (0, 0, 1) plan.

For example, a plane intercepts the crystallographic axes at (1, 1, 1), as shown in Fig. 1.13. Therefore, the Miller index of this plane is (111).

#### Example 1.2.

Find the Miller index for the plane that parallels to the x-y plane, as illustrated in Fig. 1.14. The intercepts of this plane with the three axes are  $(\infty, \infty, 1)$ . Taking the reciprocal of each number results in (0, 0, 1). Therefore the Miller index of this plane is (0, 0, 1). The direction, normal to the (0, 0, 1), is written as [0, 0, 1]. In the case of cubic crystals, (0, 0, 1), (1, 0, 0), or  $(0, 0, \overline{1})$  are crystallographically identical, and they are generalized as  $\{001\}$ .

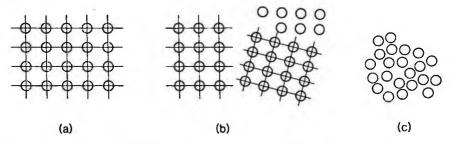

One may imagine that the different crystallographic planes give different atomic packing densities. Substrate  $\{1, 0, 0\}$  is most commonly used for metal oxide semiconductor (MOS) device manufacturing owing to its low surface state density. Substrates  $\{1, 1, 1\}$  are most often used for bipolar device manufacturing. The  $\{1, 1, 1\}$  substrate has a higher oxidation rate as compared to  $\{001\}$  owing to its high atomic packing density. Furthermore, it is less prone to channeling during ion implantation.

#### 1.5. Wafer Processing Flow

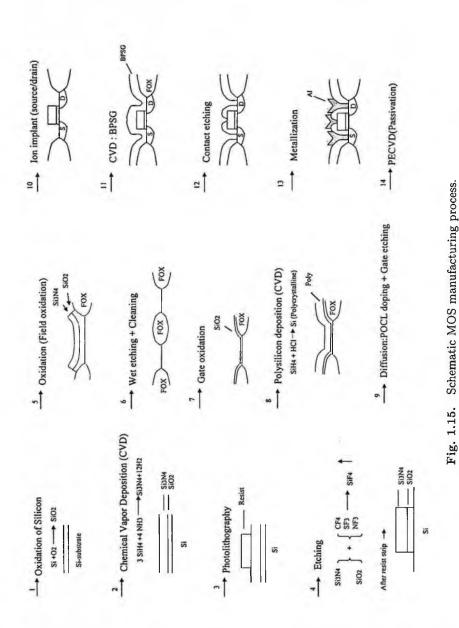

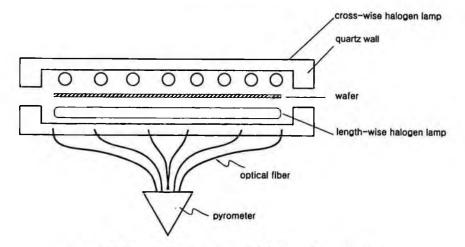

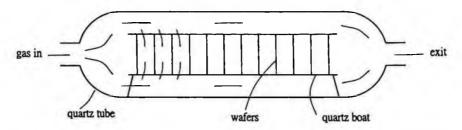

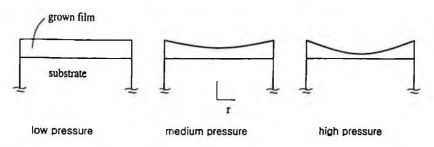

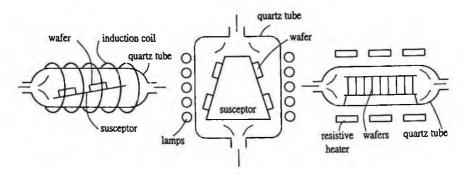

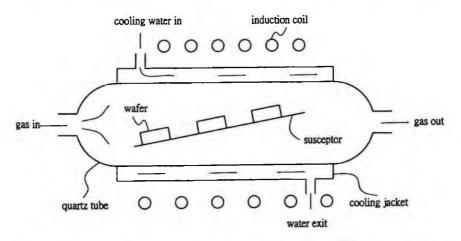

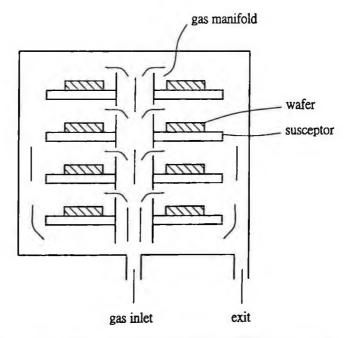

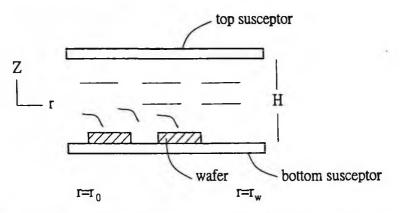

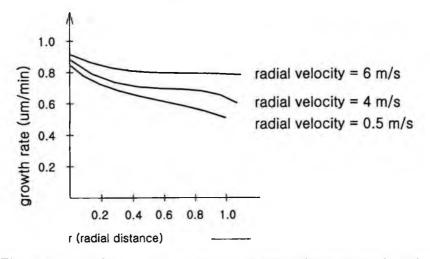

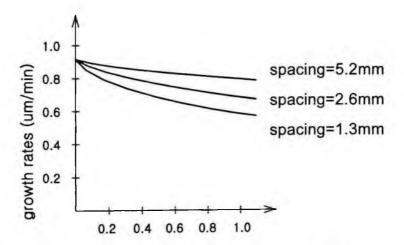

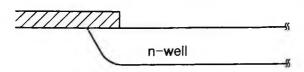

For the purpose of illustrating the wafer process module principles, a simplified process flow for making a MOS transistor is shown in Fig. 1.15. The wafer processing often starts with growing a silicon epitaxial layer. Using an epitaxial wafer substrate is optional for device manufacturing. An epitaxial growth process is to grow a single crystalline thin film on a single crystalline substrate. The reason for using this process is two fold. First, the epitaxial growth results in a purer silicon film, free of carbon and oxygen, for device manufacturing. Second, one can grow a lightly doped film on a heavily doped substrate to achieve a higher breakdown voltage, while minimizing the power dissipation in the substrate. The epitaxial growth is conducted in a cold-wall chemical vapor deposition reactor at atmospheric pressure.

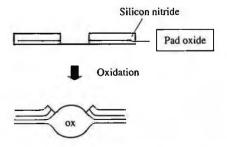

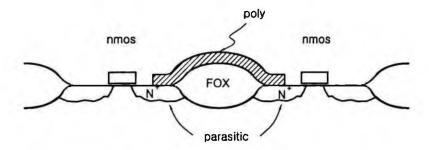

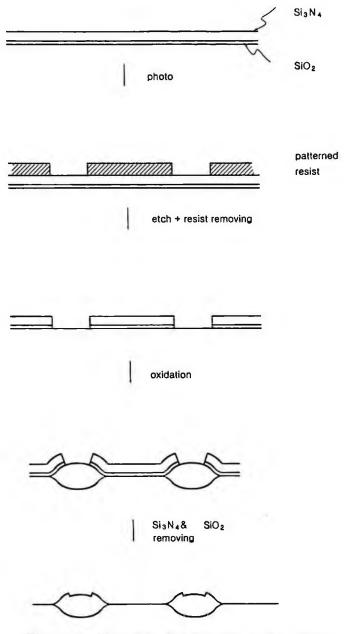

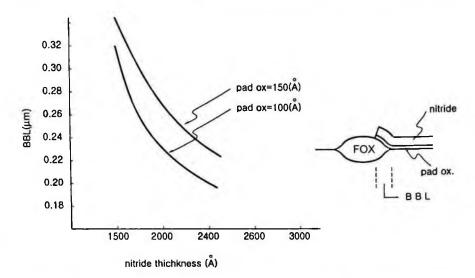

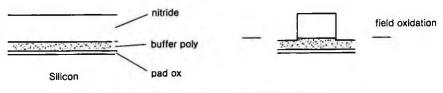

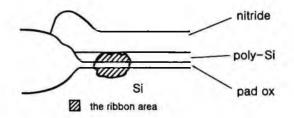

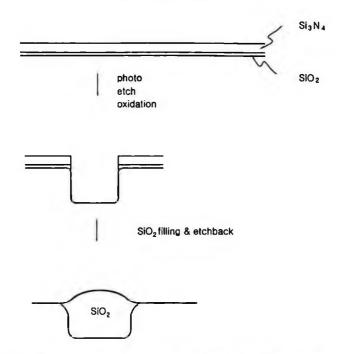

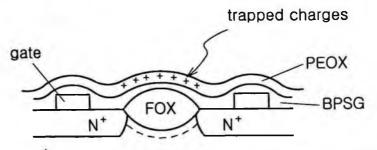

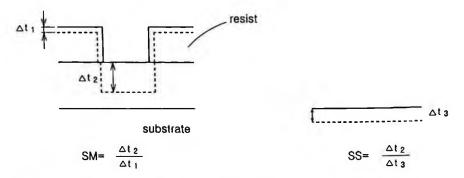

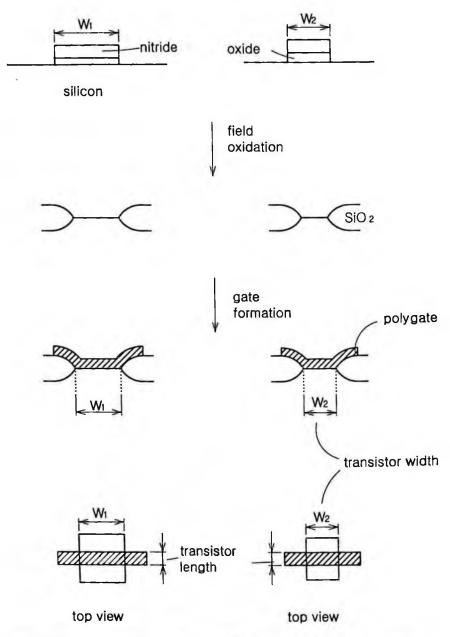

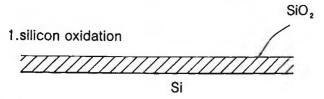

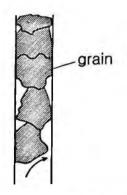

For planar silicon process technology, it is essential to form local isolation (oxide islands) around each individual device so that each can function independently. To form the isolation islands, one must first form a patterned silicon oxide and silicon nitride stack. The silicon nitride has a very slow oxidation rate, and therefore it can be used as oxidation masks. However, the silicon nitride has such a high stress level that when directly deposited atop the substrate, it will damage or even crack the substrate. A stress buffer, such as silicon dioxide, must be deposited between the nitride and the substrate.

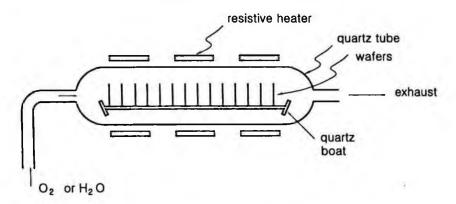

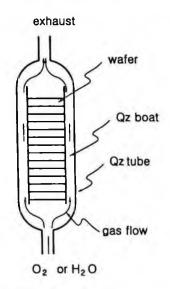

To form silicon oxide, the silicon wafers are placed in a furnace system in an oxygen or steam ambient:

$$Si + O_2 \longrightarrow SiO_2$$

.

The oxidation rate is a function of temperature, silicon surface orientation, and oxidation time. On top of the silicon oxide, a chemical vapor deposition is conducted to form a thin silicon nitride film.

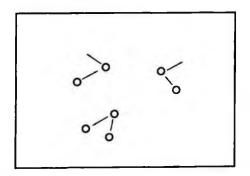

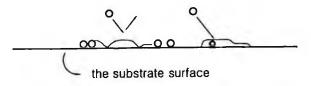

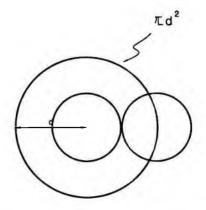

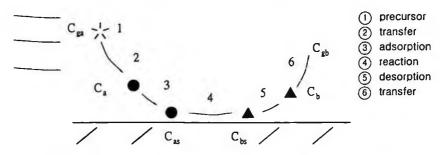

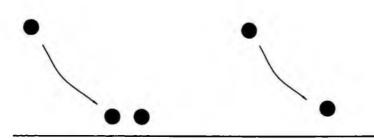

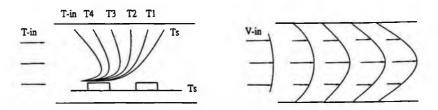

Chemical vapor deposition (CVD) is a process in which a precursor gas mixture passes over a heated substrate and thereby chemical reactions are initiated in the vicinity of the heated substrate, and a nonvolatile solid film is formed. CVD has been widely used in semiconductor manufacturing to deposit both conductive films, such as tungsten and tungsten silicide, and dielectric films, such as silicon nitride and oxide. For the silicon nitride, the reaction proceeds as follows:

$Si + NH_3 \longrightarrow Si_3N_4$ .

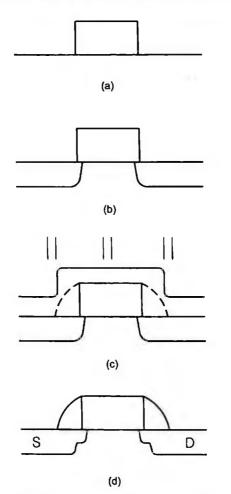

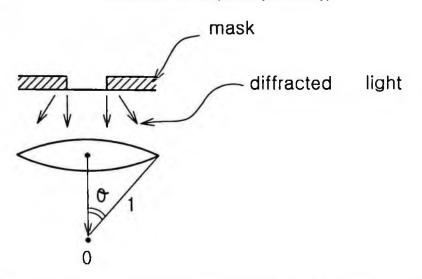

Now that the oxide-nitride stack is formed, the next step is to define the areas where the silicon oxide is to be formed. This is accomplished by using photolithography, which delineates the areas where the nitride has to be removed for the underlying silicon surface to be oxidized. The photolithography process is often followed by an etching process, in which the material in the undesired area is removed.

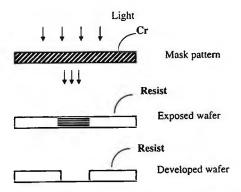

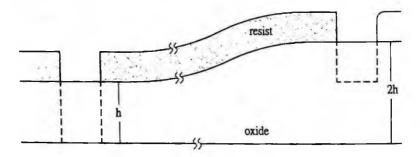

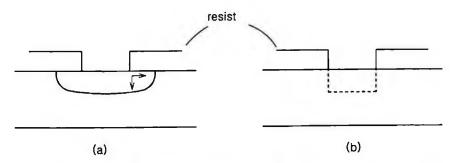

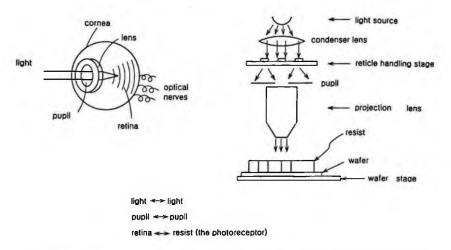

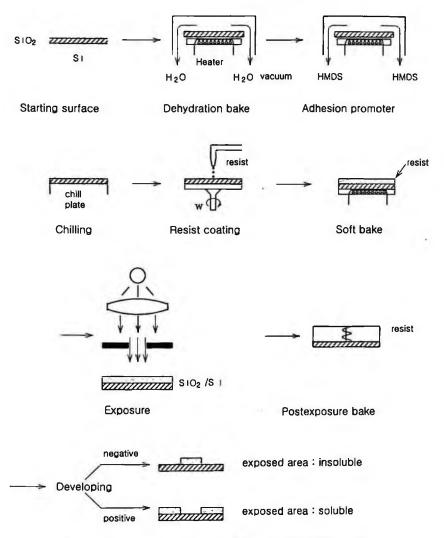

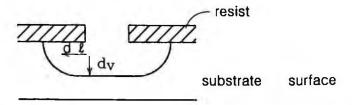

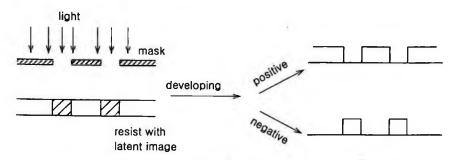

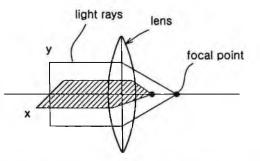

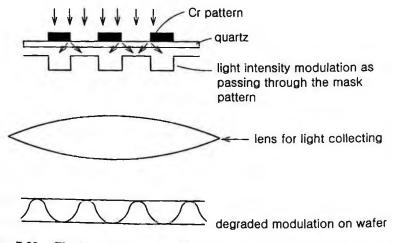

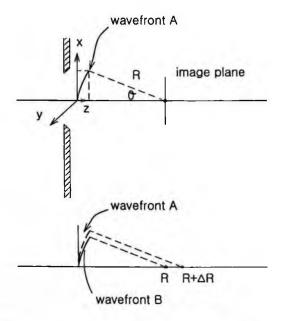

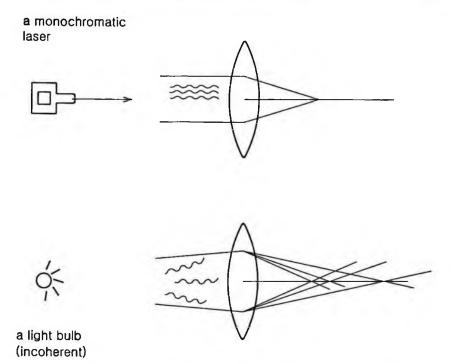

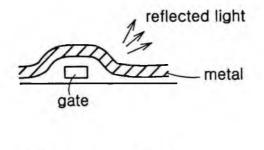

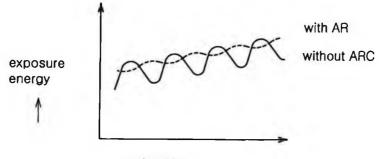

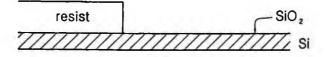

Photolithography involves complicated photochemical reactions. First, wafers are spin-coated with a photo-active polymer, which turns soluble in an alkaline solution on exposure to light. The exposure light illuminates on a photomask and incident on the polymer-coated wafer surface, generates the desired latent images. On developing with the alkaline solution, the mask pattern is transferred to the wafer surface, as illustrated in Fig. 1.16. Two important

Fig. 1.16. Transferring mask patterns onto the wafer surface by using photolithography.

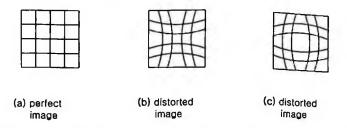

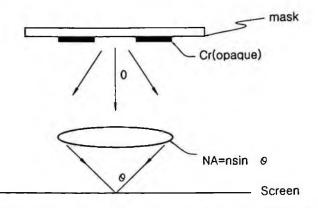

performance indices in the photolithography process are resolution and depth of focus. Both are related to the wavelength of the exposure light source and the sizes or numerical apertures of the lenses.

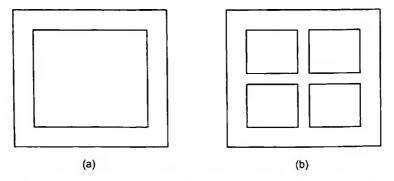

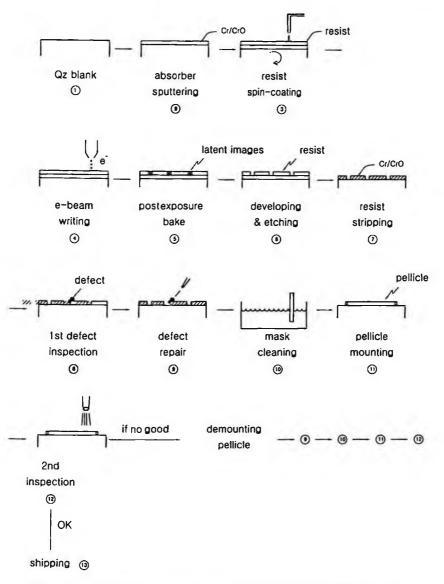

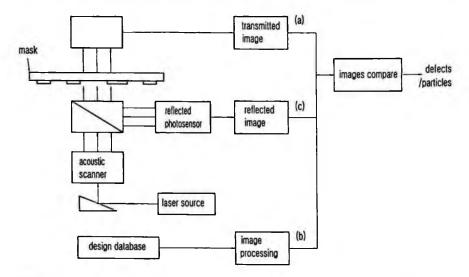

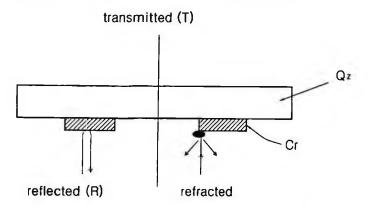

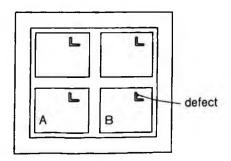

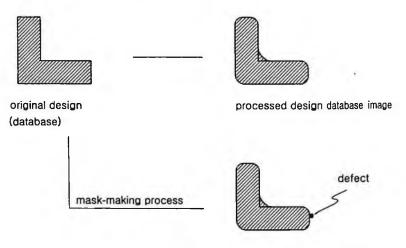

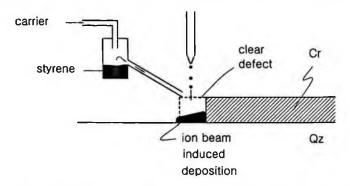

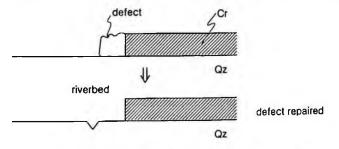

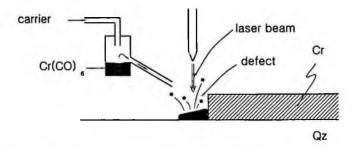

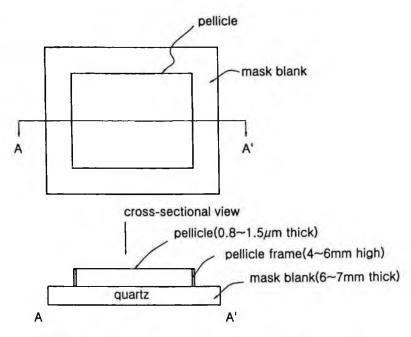

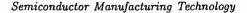

Photomasks are chrome patterns on the nearly optically impeccable quartz substrates. The chrome indicates the opaque area, and the quartz indicates the transparent areas. To generate a mask layer, a resist-coated chrome on a quartz blank is exposed to an electron beam, which is driven by the data file from the design layout information. Each local pattern is composed of a large number of electron beam shots. For advanced masks, the number of shots for one mask layer can be as large as billions. The exposed blank is then developed and etched to render the chrome patterns on the quartz. The etched pattern is then inspected using inspection machines, which compare the written pattern to the original data file or compare one die to the next die to assure that the pattern is perfect. Should any differences be detected, they are treated as defects, and they must be removed with a repair tool. Finally, a pellicle is mounted on the mask to protect the pattern from mechanical scratches and to make particles on the pellicle surface unprintable.

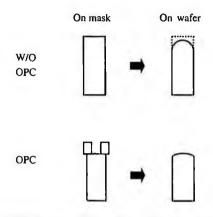

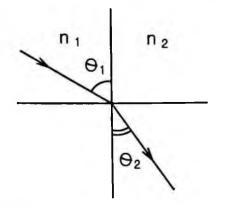

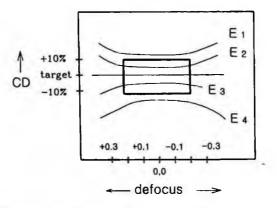

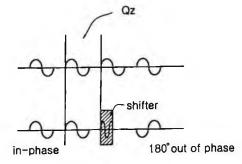

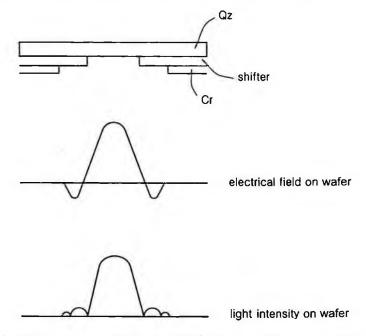

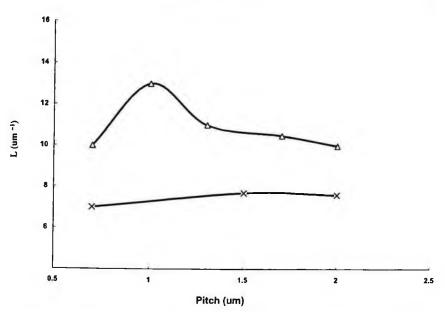

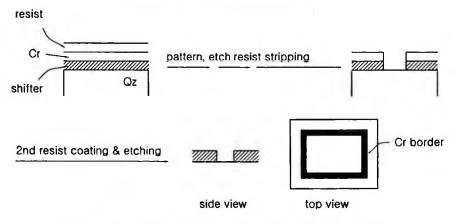

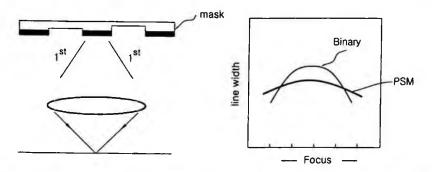

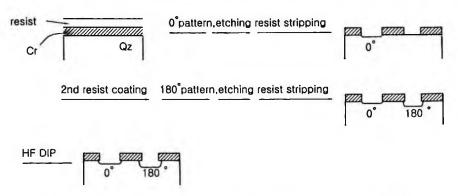

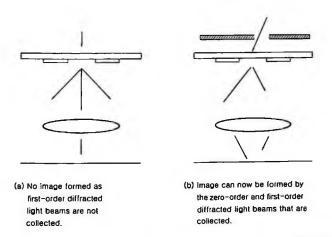

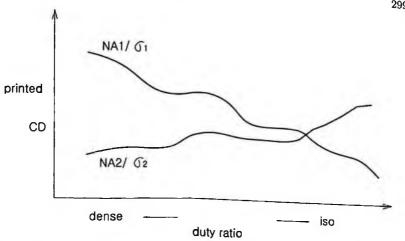

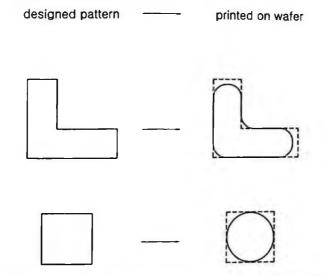

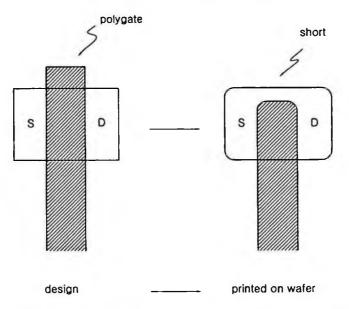

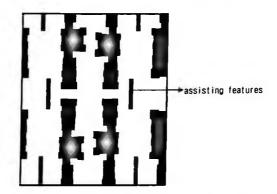

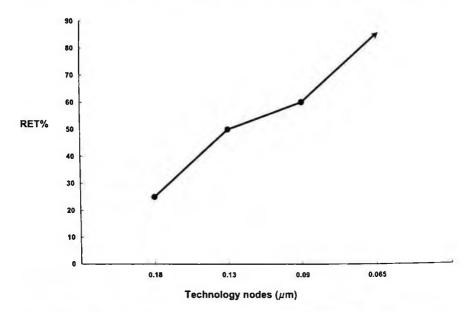

Resolution enhancement technology (RET) is required to enhance the photolithography performance owing to the fact that the operating wavelengths do not evolve as fast as the geometry shrinking pace. The most commonly seen RET includes phase shifting masks (PSMs) and optical proximity correction (OPC) techniques. Phase shifting primarily takes advantage of the fact that a partially transparent film with a certain refractive index can shift the phase of the light that comes out of the material. Consequently, by deliberately choosing a film thickness such that the shifted and nonshifted lights are of the opposite phases (180 degrees), the pattern image contrast can be significantly enhanced. OPC is an empirical technique in which the originally designed patterns are altered in such a manner that the printed patterns on the wafer can be matched to those of the originally designed ones, as shown in Fig. 1.17.

Up to this stage, a plasma etching is required to remove the silicon nitride that is not covered with the resist. A plasma etching is a material removal step. Energetic electrons in a plasma system (a partially

Fig. 1.17. Without OPC, severe line-end rounding is observed; with OPC, the rounding is improved.

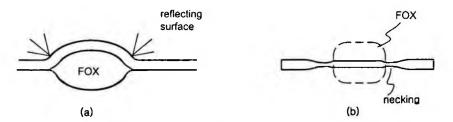

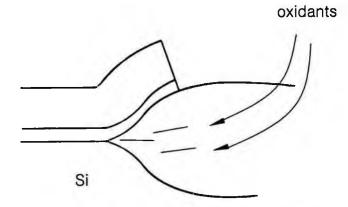

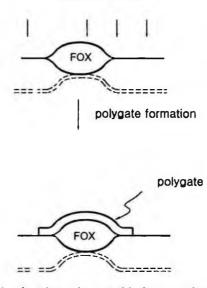

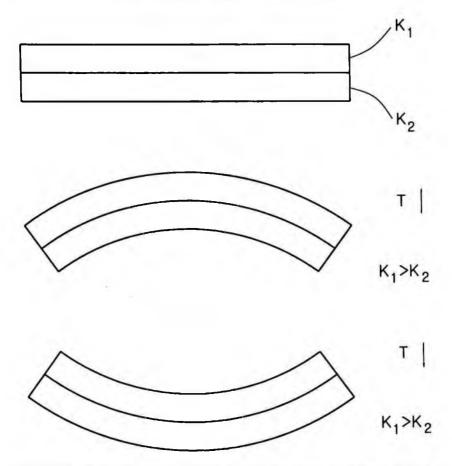

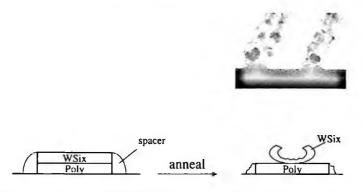

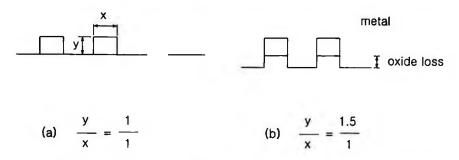

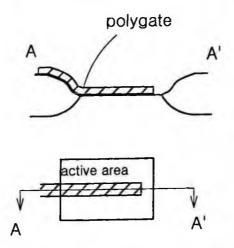

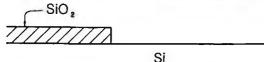

ionized gas system) generate highly reactive free radicals, which react with solid surface and form volatile reaction products, thereby removing the surface material. Obviously, to remove the nitride and form the oxidation mask pattern, one must choose the proper chemical to react with the nitride but not with the resist material. After the etching, the resist is removed with a sulfuric acid solution. The wafers with the nitride-defined patterns are sent into a high-temperature furnace for field oxidation. The silicon volume expands as the oxidation reaction proceeds. Consequently, the nitride edge is bent, as illustrated in Fig. 1.18. The field oxide's thickness ranges from 3500 to 6000 Å. When the field oxidation is accomplished, the nitride and

Fig. 1.18. After oxidation, the oxide volume expands, causing the nitride stack edge to bend.

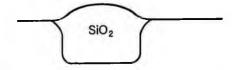

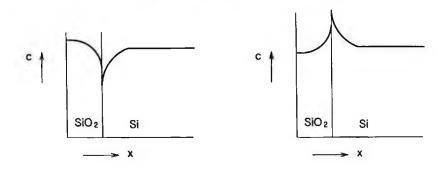

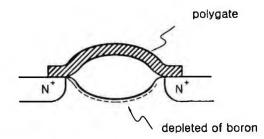

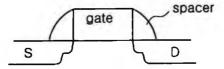

oxide are removed with hot phosphoric acids and an HF solution, respectively, leaving the silicon surface with scattered oxide islands. To form devices, gate oxidation is first conducted to form a thin layer of high-quality oxide for the MOS transistors, followed by the CVD process of polysilicon deposition. The deposited polysilicon is highly resistive and must be doped to reduce its resistance.

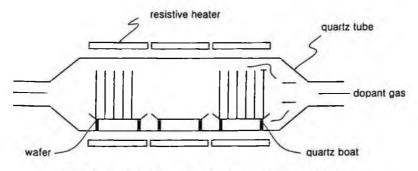

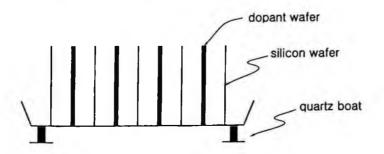

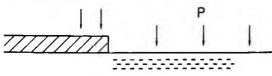

The doping process is accomplished through dopant diffusion in a high-temperature furnace. Precursor gas is introduced into a hightemperature furnace, where it converts into dopant atoms, such as P or B, on the substrate surface. The atoms are then driven by thermal energy into the substrate to change the intrinsic polysilicon to doped polysilicon. The resistance change depends on the amount of introduced dopants. Applying photolithography and etching to selectively remove the polysilicon material, one can form gate and interconnect structures. The gate can be used for the ensuing selfaligned source and drain ion implantation.

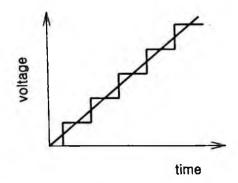

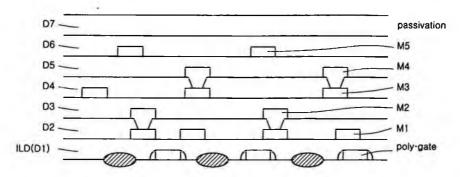

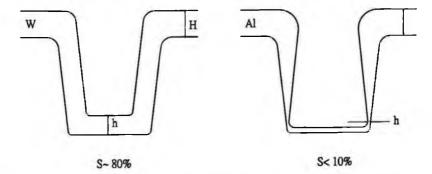

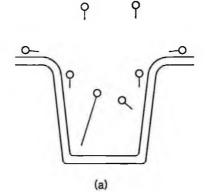

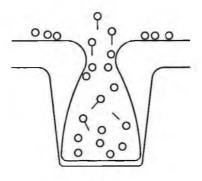

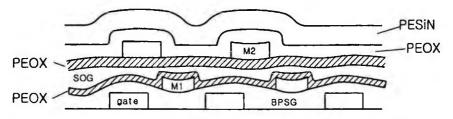

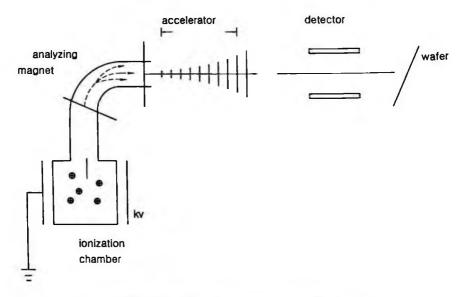

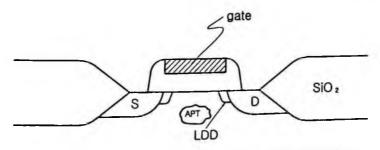

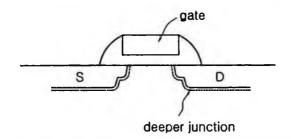

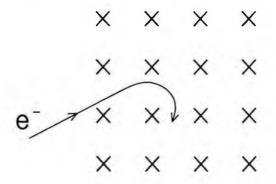

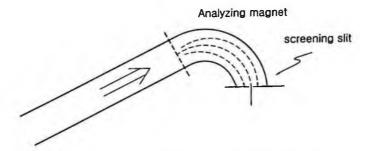

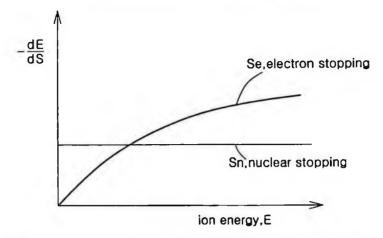

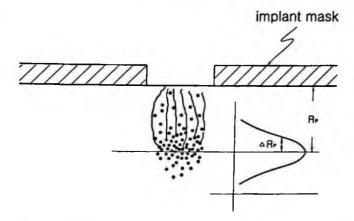

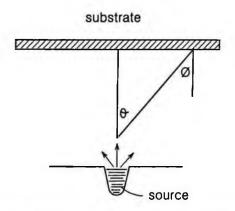

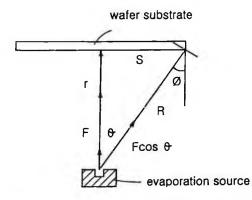

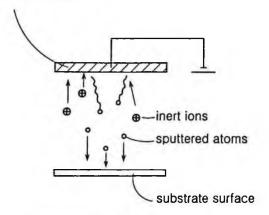

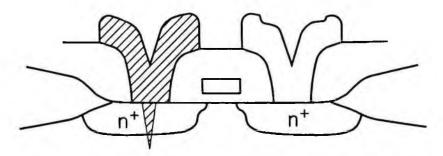

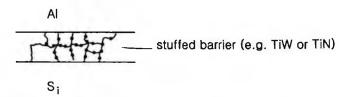

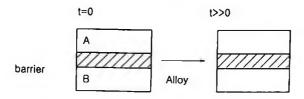

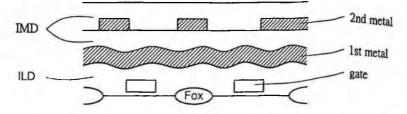

Ion implantation is the process of doping the substrate in a precise manner. Dopants are ionized and extracted from an ionization chamber into an accelerator. The ion beams are accelerated to a certain high energy level and steered electromagnetically toward the substrate surface. With the accelerated energy, the ions penetrate into a substrate with certain depths. With a fixed ion-substrate pair, the higher the implant energy, the deeper the ion penetrating depth. After the source and the drain are implanted and annealed, the MOS device structure is pretty much complete. One has the source, drain, and gate. Each device is isolated from its surroundings with the field oxide islands and is capable of functioning individually. The process thus far is often called the front-end process. From this step, all the subsequent process steps are often called the back-end process and are supposed to connect these devices together to fulfill the circuit functions. Theoretically, one layer of metal can connect all the MOS transistors together and form a meaningful circuit. However, considering the packing density and line resistances, there is a tendency to use more than one layer of metals. The state-of-the-art 90-nm circuits are often composed of up to eight or ten layers of metals. To form the first-level connection, a thick dielectric layer is deposited. Holes on the dielectric layer are opened up by using photolithography and etching. The connecting material, usually aluminum for technologies of larger than  $1.0 \,\mu$ m, is sputtered onto the substrate.

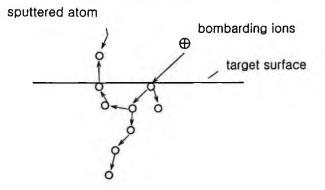

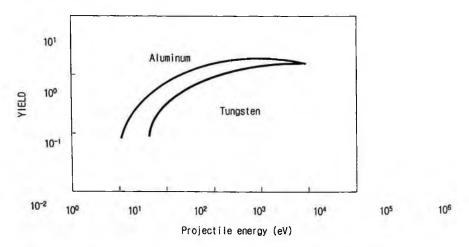

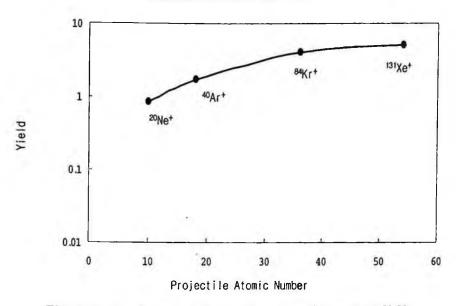

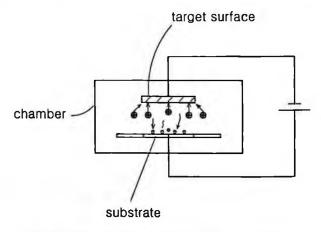

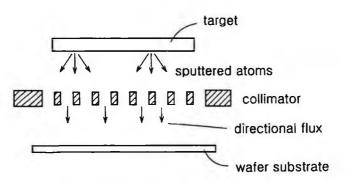

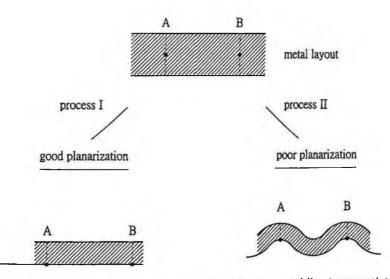

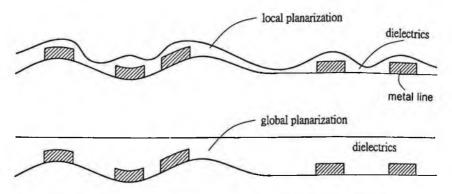

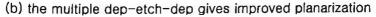

Sputtering is a process conducted in a plasma system. Heavy inert ions, such as argon, are accelerated toward a target material, knocking out the surface atoms, which then fall and land on a wafer surface. The deposited metal layer is then defined with photolithography and etching. Aluminum layers of 5000 to 15000 Å are often required to form a proper metal interconnection. For a multilayer metal structure, it is very critical to maintain a proper planarization for the subsequent metal layers to form. Planarization plays a vital role in the back-end process.

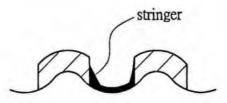

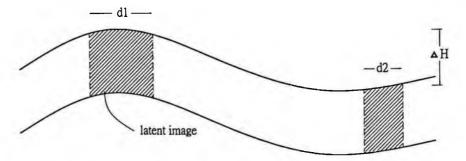

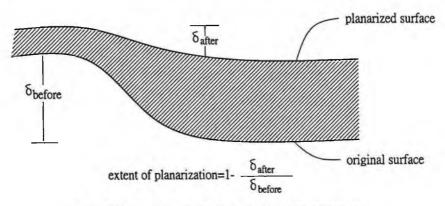

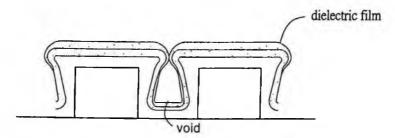

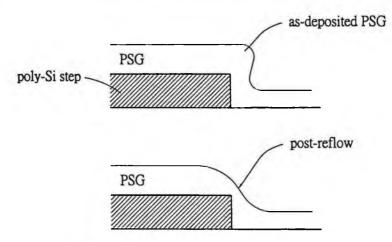

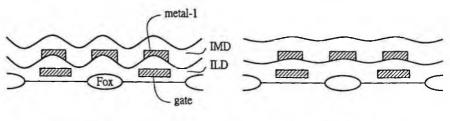

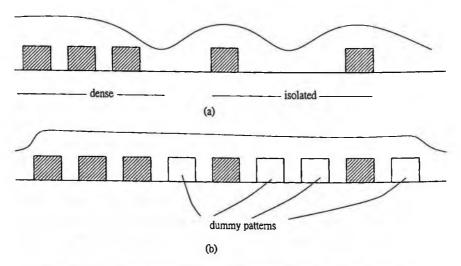

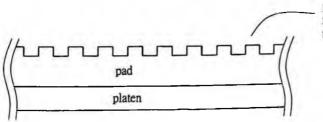

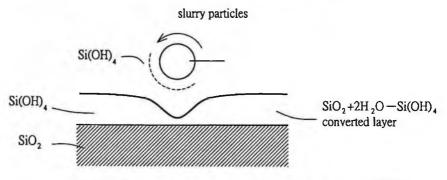

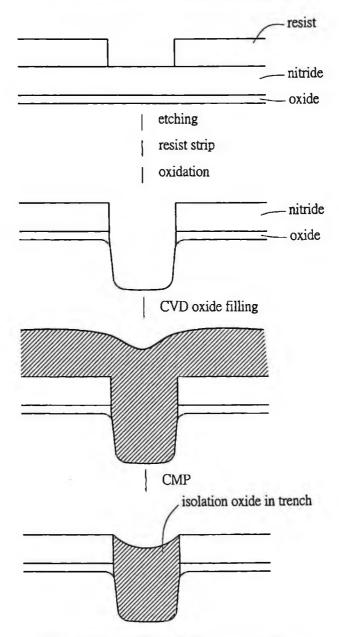

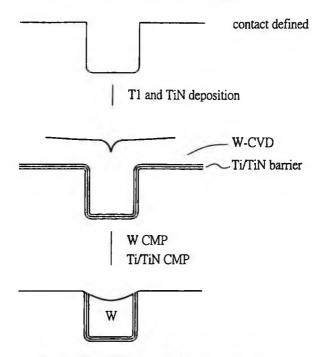

Planarization is a technique to planarize the wafer surface and facilitate the ensuing process steps. A nonplanar surface is more prone to cause after-etching metal residues, high metal resistances, and poor photolithography performance. There is a wide variety of planarization techniques, ranging from high-temperature flow-, to spin-on-glass, etch-back, and CMP. For inter-metal isolation and planarization, a layer of silicon dioxide or its derivatives needs to be deposited. The final process step in making the device is to deposit a passivation layer, a silicon oxide on nitride stack. It prevents the device from mechanical scratches and mobile ion contamination. Because the deposition process occurs on top of an aluminum layer, the process temperature is limited to below 350°C to maintain the metal's integrity. As a result, the plasma-enhanced chemical vapor deposition (PECVD) technique is used.

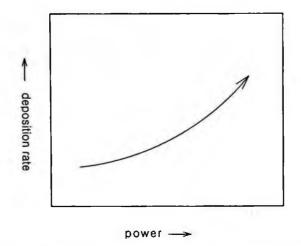

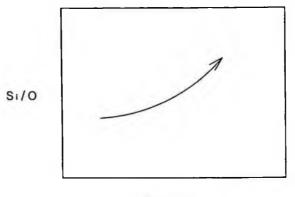

PECVD is a film deposition process in which the precursor gas is dissociated into highly reactive radicals by the energetic electrons in plasma. The reactive radicals react with each other and deposit onto the substrate surface to form a nonvolatile film at low ambient temperature. The resulting films are often amorphous and nonstoichiometric in nature.

The above text elaborates the basics of process modules that are needed for making MOS devices. The actual manufacturing can be far more complicated, and it involves repetitive use of each module. The modules also evolve with technology migration. For example, as a device shrinks, the packing density increases, and more devices can be packed into a unit area of the silicon surface; long interconnects are inevitable. For long interconnects, the RC delay is doomed if no alternative approaches are taken. Copper has a far lower resistance than aluminum, and it is used as an alternative to aluminum. On the other hand, copper was not used until CMP became available because it is not plasma etchable. To further lower the RC delay, low dielectric constant materials are needed in addition to the lower interconnect resistance. Silicon dioxide is often doped with F or C to lower its dielectric constant.

# 1.6. What is the Semiconductor Industry Trying to Achieve?

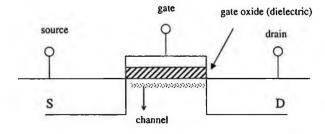

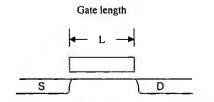

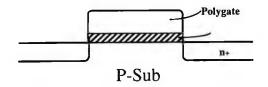

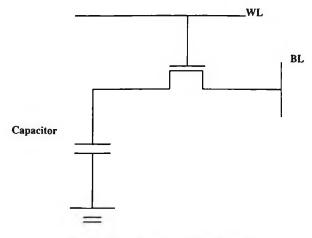

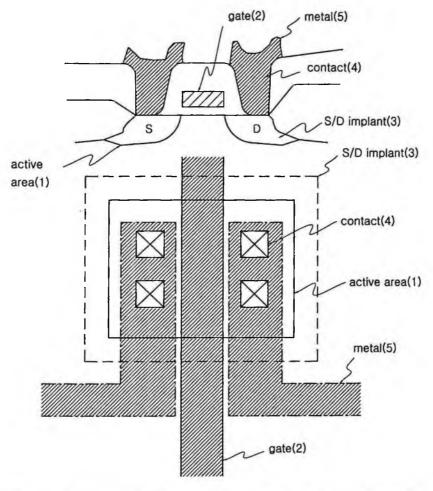

The entire semiconductor industry pivots on one device, MOS transistor, as shown in Fig. 1.19. In other words, the industry is focusing on making circuits with MOS transistors and on shrinking the circuit feature sizes so as to give more powerful and faster circuits with lower cost.

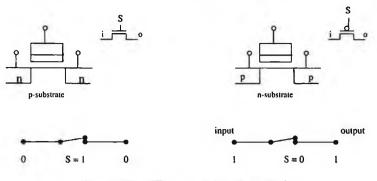

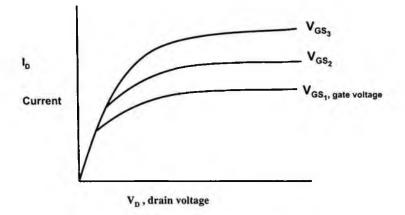

There are two types of MOS transistors, the NMOS and PMOS. In the case of an NMOS device, the source and drain are commonly phosphorous-doped (*n*-type, rich in electrons) on the *p*-type substrate (rich in holes). If one sets both the source and the drain at grounded states, then by changing the applied voltage to the gate from positive to zero, for example, 5 V or state 1, to 0 V or state 0, one can turn the conducting channel on and off. When the conducting channel is

Fig. 1.19. An MOS transistor.

Fig. 1.20. The n-switch and p-switch.

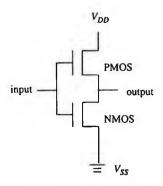

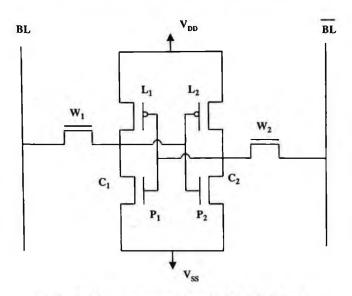

on (at state 1), switching the drain from ground to any positive voltage (typically 5 V) would force electron flow from the source to the drain. Now, if we consider the source as the input and the drain as the output, then the NMOS device can function as an *n*-switch. If the gate is at 0, the channel is turned off. If the gate is at 1, the channel is turned on, and the state of the source (input) can be transferred to the drain (output). Analogously, one can explain the operation of a *p*-switch, as shown in Fig. 1.20. The switches are the fundamental building blocks for constructing complicated ULSI circuits. For example, by connecting the *n*- and *p*-switches end-to-end, and by tying the gate together, as shown in Fig. 1.21, one can obtain an inverter. Table 1.6 shows the inverter truth table. Various combinations of the switches can be made to represent various Boolean truth

Fig. 1.21. A complementary switch.

| Table 1.6.<br>table. | Inverter truth |  |

|----------------------|----------------|--|

| Input                | Output         |  |

| 0                    | 1              |  |

| 1                    | 0              |  |

tables that can develop into ULSI circuits such as logic, memory, imaging processor, and microprocessor chips.

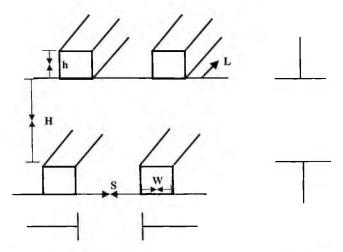

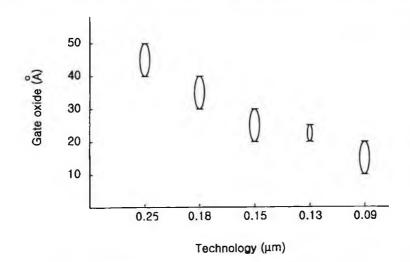

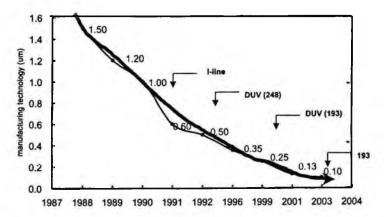

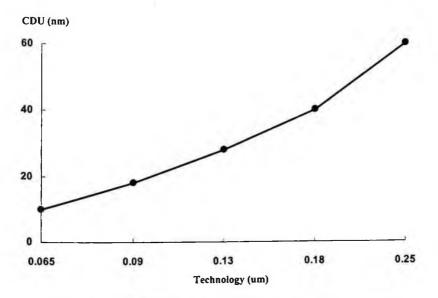

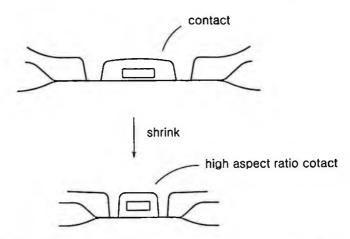

Ever since it was learned how to put a large number of functional circuits on a silicon wafer by using planar processing technology, a real race began. The industry has been pushing for faster, cheaper, and higher-packing-density chips. Shrinking the chips both in horizontal and vertical dimensions is the only way to achieve all three goals. In the semiconductor industry, the feature sizes of an IC circuit are defined by a set of dimensions, called design rules. These rules are proposed by those who know the process technology capabilities and limitations. The technology nodes, or the manufacturing technology, as we will use in the ensuing contents, for example,  $0.5 \,\mu\text{m}$ ,  $0.35 \,\mu\text{m}$ , or 0.18  $\mu$ m, are referring to the transistor gate length. The gate length is the length of the gate in the current flow direction, as indicated by L in Fig. 1.22. Table 1.7 shows the critical feature sizes of 0.5- $\mu$ m versus  $0.35-\mu m$  production technology. Approximately, each feature is shrunk by a factor of 70%. The shrinkage in the device geometry calls for a change in process technology.

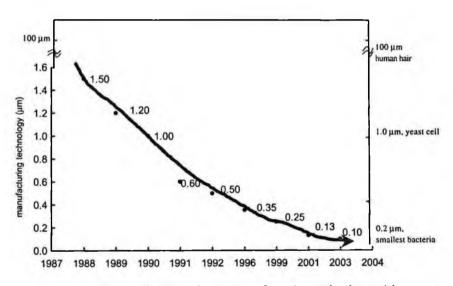

Figure 1.23 shows the technical evolution compared to the commonly known objects. Beginning in the early 1960s, the industry was making circuits with a characteristic length (most commonly referred to as the gate length) of  $10 \,\mu$ m. In the year 2002, the worldwide

Fig. 1.22. The MOS transistor gate length.

Table 1.7. The critical feature sizes of  $0.5-\mu m$  versus  $0.35-\mu m$  technology. A 70% shrinking path (units:  $\mu m$ , line width/space).

|                  | $0.5\mu{ m m}$ | $0.35\mu{ m m}$ |

|------------------|----------------|-----------------|

| Gate length      | 0.5/0.5        | 0.35/0.35       |

| 1st contact hole | 0.6/0.6        | 0.4/0.4         |

| 1st metal layer  | 0.7/0.65       | 0.45/0.45       |

| 2nd contact hole | 0.7/0.7        | 0.5/0.5         |

| 2nd metal layer  | 0.7/0.65       | 0.45/0.45       |

| 3rd contact hole | None           | 0.6/0.6         |

| 3rd metal layer  | None           | 0.7/0.7         |

Fig. 1.23. Evolution of semiconductor manufacturing technology with respect to the known objects.

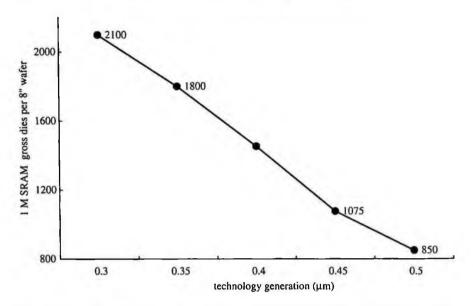

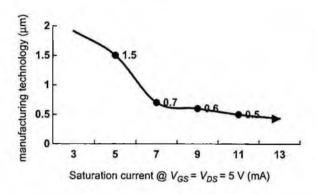

semiconductor industry was running a 0.13- $\mu$ m technology for production. The 0.13- $\mu$ m is much smaller than the size of a virus cell and measures only hundreds of atoms across. Figure 1.24 shows the gross number of dice that can be made per an eight-inch wafer for a 1-M (megabit) static random access memory (SRAM). By using 0.5- $\mu$ m processing technology, one can have about 850 dies per eight-inch

Fig. 1.24. The gross dies per wafer for 1-M SRAM made with different technology generations.

wafer. It will have about 1800 dies per eight-inch wafer when shrunk to 0.35-µm processing technology. The increase on dies/wafer is over 50%. Therefore the cost per die can be reduced by approximately 50%, assuming that the process cost does not increase significantly. Because the transistor gate length is scaled down by 70%, the circuit speed will significantly increase as well. Figure 1.25 indicates that the transistor saturation current increases as the gate length is scaled down. The device speed increases with the saturation current. Furthermore, one can clearly see from Fig. 1.3 that owing to the shrinkage from  $0.8 \,\mu\text{m}$  to  $0.4 \,\mu\text{m}$ , one can use a  $0.4 \,\mu\text{m}$  technology to make a 64-M DRAM of 180 mm<sup>2</sup>, as opposed to using  $0.8 \,\mu m$  to make a 16-M DRAM of 130 mm<sup>2</sup>. It is clear that the die area does not increase proportionally with the memory sizes due to technology migration. The shrinkage nearly triples the packing density. To shrink the device is much more involved than it appears. Sometimes, it extends the applications of existing module technologies, and other times, it requires new module technologies.

Fig. 1.25. Saturation current, directly related to device speed, increases as gate length shrinks.

As a result of the devices shrinking, more chip functions with faster speeds can be packed into a tiny chip at a lower cost. Consequently, applications of semiconductor devices have been multiplying over the last 50 years. The applications are so widespread that semiconductors affect almost all facets of our daily lives, ranging from computer information systems, communications, entertainment, and medical instruments to automotives. As the semiconductor technology continues to improve and advance, it will certainly result in wider and more powerful applications at lower prices.

## 1.7. The Never-Ending Effort — Yield Improvement

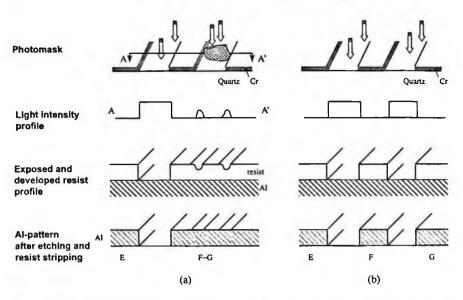

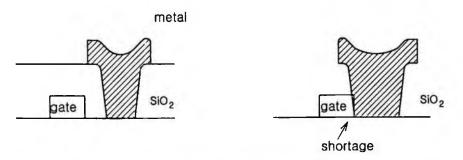

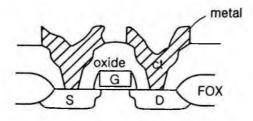

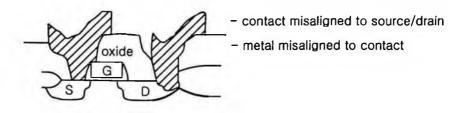

As the device geometry approaches the range of one-tenth of a micron, its functionality and yield strongly correlate to the cleanness of the manufacturing environment and its incoming materials. Any size of particles or contaminants that fall on a device during its manufacturing process can cause the device to become dysfunctional. Figures 1.26–1.28 illustrate that there are several cases in which particles can reduce yield:

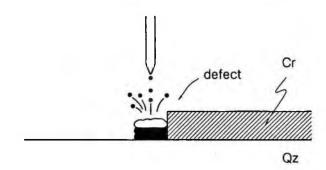

(a) A particle falls on a mask, causing printable defects, and extra patterns show up on the wafer, as shown in Fig. 1.26.

Fig. 1.26. (a) A particle on mask causing metal lines, F and G, to bridge, and (b) a clean mask gives three clear-cut metal lines: E, F, and G.

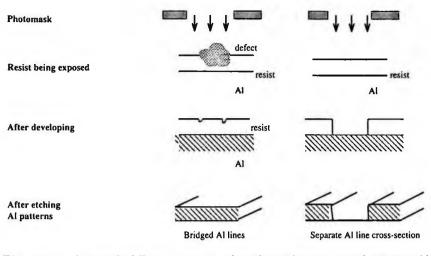

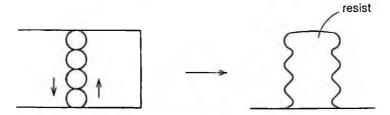

- (b) A particle falls on a resist layer, preventing the resist from being exposed and hence causing the underlying conducting layer to be electrically shorted, as illustrated in Fig. 1.27.

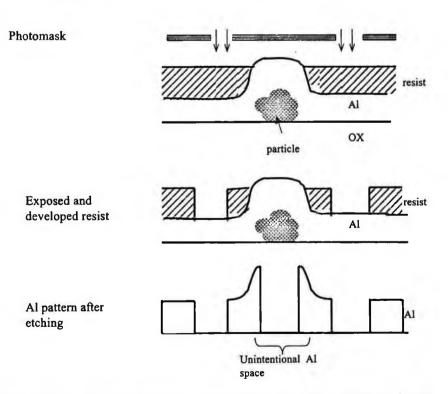

- (c) A particle falls on an oxide layer prior to the metal deposition process, causing a bump, which is etched away. This will result in a metal line opened electrically, as demonstrated in Fig. 1.28.

The defects on a wafer at any stage of the wafer processing can be detected by wafer defect inspection machines. It should be noted that not every defect would lead to wafer yield loss. However, to achieve high wafer yield, it is necessary to keep the defect count on a wafer as low as possible. The following equation is often used to correlate defect density and the wafer yield:

$$Y=\frac{1}{(1+DA)^m}\,,$$

where m represents the complexity of the manufacturing process and A represents the die area. In addition, D represents the defect density,

Fig. 1.27. A particle falls on a resist surface that is being exposed, causing Al lines to bridge under the particle.

Fig. 1.28. Al line open owing to a particle under the Al line, causing a bump.

which is not necessarily equal to the defect count, as inspected by defect inspection machines. Rather, it is a number that characterizes the cleanness of a process line. The wafer yield, Y, equals the ratio of the final total number of good dies to the total number of dies made on the same wafer.

The defects come from various sources. To obtain a good wafer yield, the defect level needs to be kept as low as possible. The important aspects essential to achieving low defect levels are discussed as follows:

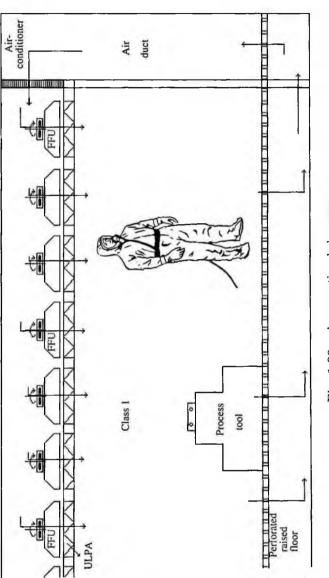

(a) The clean room environment. A clean room setup is a basic requirement for making semiconductor devices. Depending on the final device geometry, the cleanness (the class) requirements of the clean room could be different. For a class 1 clean room, the specification requires that the number of particles that are larger than 0.5  $\mu$ m be less than one in a cubic foot space. Figure 1.29 shows a schematic of a conventional clean room. The air pressured by a fan filtering unit (FFU) goes through an ultra low penetrating air (ULPA). The ULPA has an efficiency of 99.999% in filtering 0.1- $\mu$ m particles. In other words, only one out of 100 000 0.1-µm particles can penetrate through the ULPA. The filtered air flows downward in a laminar flow fashion so as not to disturb any more particles from the equipments and table surfaces or dead corners. The working tunnels stand on a raised grid floor to allow for continuous air circulation and filtration. In the air duct, there are air-conditioners that control the air temperature and humidity. Typically, a clean room is controlled at  $45 \pm 3^{\circ}$ C and  $45 \pm 5\%$  relative humidity. In addition, the particles, if generated in the working tunnels, can be carried down the grid floor and circulated toward the ULPA, and therefore fresh air (free of particles) is regenerated.

(b) Inappropriate process steps. For example, during a cleaning process, the wafer goes through acid and base solutions. If one or the other solution is not thoroughly rinsed, the reaction of the acid and base will result in salt formation, which often leads to particles. Particles can be generated in processing equipment as well. A moisture

leak or an aging O-ring in a plasma chamber can result in particle formation. Process monitoring and equipment maintenance are critical in maintaining a clean semiconductor manufacturing line.

(c) Contamination from personnel. Particles can be generated from human bodies such as hair, cosmetics, perspiration, or saliva. There are two methods to keep an environment clean. One is to wrap the wafers, and the other is to wrap people. All personnel working in a clean room are required to wear clean gowns and breathing masks, as shown in Fig. 1.29. The air that is breathed out must be filtered before it is released to the ambient. This type of clean room gear is very uncomfortable. In a SMIF environment, each machine is equipped with a mini-environment chamber. People are not required to wear clean gowns similar to those shown in Fig. 1.29. Also, no out-breathing filtering mask is required. Therefore, it is far more comfortable for humans. Discipline in gowning is crucial in controlling the clean room environment.

(d) Chemicals and water quality. To manufacture IC of nanometerrange geometry, one has to be very stringent on the quality of the supply water and chemicals. For water, there are a few items to be noted, including organics, colloids, organisms and particulates. Humic and fulvic acids are often the organics that are seen in water, with molecular weights ranging from several hundreds to thousands g/mole. Colloids are aggregates of molecules with sizes ranging from 50 to 20000 Å, and are invisible under microscopes. Organisms in water include bacteria, fungi, and viruses. The sizes are between 0.3 and  $30 \,\mu\text{m}$ . For chemicals, particle counts and sizes are major concerns. The above-mentioned contaminants can be removed using various techniques. Ion exchangers can be used to remove ionic species and particulates that are larger than  $5\,\mu$ m. Powered ion exchangers can remove even smaller particulates. Some organics and colloids (aggregates of molecules) can be separated from the liquid using polymer adsorbents or activated carbons. Membranes with different pore sizes are often used to remove ionic and organic species. The pore sizes of the membranes are the key to their effectiveness in the removal process.

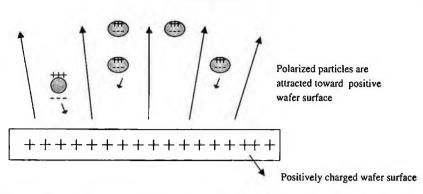

Fig. 1.30. A positively charged wafer surface can polarize particles, which are then attracted toward the wafer surface.

(e) Electrostatics in clean rooms. Electrostatic charges exist in clean rooms and can possibly result in wafer particle contamination or burnt-out circuits. A silicon wafer can charge up heat, evaporation, or its friction against the wafer container. It can also be inductively charged by its neighboring wafers or process equipment. The charged wafer surface can polarize and attracts floating particles, resulting in defects on wafers, as illustrated in Fig. 1.30. Movements or actions of workers in a clean room often generate static charges. These charges, if not properly discharged, can lead to damaging effects on the circuits or defects on the wafers. There are several common practices in a clean room that reduce the electrostatic charges: (1) air ionization is an approach that applies an intensified electrical field across a sharp point or edge to ionize the air; the resulting ions are carried away by the laminar flow in a clean room; (2) grounding all conducting surfaces and human bodies to eliminate the static charges; and (3) proper humidity control. High humidity tends to decrease the static charges formation. However, a clean room cannot be operated at a high humidity level since the equipment can rust. Normally, clean rooms are operated at about 45% relative humidity.

# Chapter 2

# BUILDING BLOCKS FOR INTEGRATED CIRCUITS

Following the semiconductor overview in Chapter 1, we will now look at the fundamental concepts of semiconductors, followed by the introduction of a few building blocks that comprise integrated circuits, and their underlying principles. These building blocks include resistors, pn junctions, and capacitors. The fundamentals of a metal oxide semiconductor (MOS) will also be introduced. Finally, a few categories of integrated circuits are demonstrated, with explanations of their major features.

# 2.1. Fundamental Semiconductor Concepts

There are myriads of publications on the theories of semiconductor devices. In this section, we will review the most fundamental equations required for understanding the basics of how such devices function. In addition, we will review important terms that are cited and used daily by those in the industry.

## 2.1.1. Energy band theory and chemical bonding theory

The number of free electrons in a material is the key to its electrical conductivity. Two theories (the energy band theory and the chemical bonding theory) are often used to interpret the mechanism of material conductivity.

An atom consists of a positively charged nucleus surrounded by negatively charged electrons, which revolve around the nucleus. The nucleus includes positively charged protons and neutral neutrons. Owing to the attraction force between particles of opposite charges, each electron is acted on by the nucleus. According to Bohr's model, each electron takes a specific energy level:

$$E_n = \frac{-Z^2 m_0 q^4}{8\varepsilon_0^2 h^2 n^2} \,. \tag{2.1}$$

The energy level is related to a vacuum level, taken as zero; Z is the atomic number of the atom,  $m_0$  is the free electron mass, q is the charge of the electron,  $\varepsilon_0$  is the permitivity, h is the Planck's constant, and n is an index for the energy level.

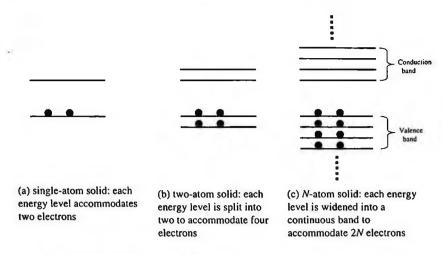

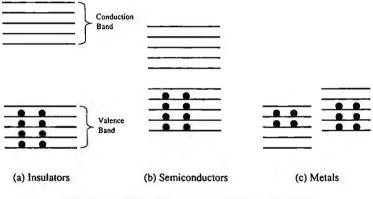

Pauli's exclusion principle requires that each energy level accommodate only two electrons. When two atoms are brought together, the electrons of each atom are influenced by the two nuclei, and the original energy level is split into a so-called modified level to accommodate four electrons instead of two. As more atoms are brought together, such as in a solid material, the energy level is widened into a continuous energy band, which accommodates 2N electrons. N is the number of atoms in the solid material, as shown in Fig. 2.1. In a solid, the electrons that are farthest away from the nuclei, or the most loosely attracted by the nuclei, are called valence electrons. The energy band that accommodates these electrons is called the valence band. No valence electrons will conduct any electric current until they are freed from the valence band and pumped into the conduction band, where they are free to move around. At 0K, the valence band is filled up with electrons, while the conduction band is empty. No electrons are allowed to take any energy levels between the conduction and valence bands; this gap is called the forbidden gap. The energy that is required to pump electrons from a valence band to a conduction band determines whether the material is a good conductor or not. For conductors, such as metals, the valence band and conduction band basically overlap, as illustrated in Fig. 2.2. On the other hand, for an insulator, the band gap is as large as several electronvolts. For example, the band gap of silicon dioxide is 8eV. Meanwhile, the band gaps of semiconductors fall in between those of insulators and conductors.

The chemical bonding theory interprets this from another perspective. In a solid, atoms are chemically bonded to each other.

Fig. 2.1. Split of energy level as the number of atoms increases.

Fig. 2.2. Band diagrams of various materials.

Silicon or germanium has four valence electrons. When the atoms are chemically bonded, they form covalent bonds; each bond requires two electrons and is formed with one electron from each atom. No free electrons are available to conduct electric current until some of the bonds are broken by external forces. Each dissociated covalent bond generates two free electrons, which are subject to external electrical fields that force the electrons to move around and conduct current.

The amount of energy that is required to break a chemical bond is called bond dissociation energy. The band gap energy corresponds to the bond dissociation energy. The electrons resulting from the broken bonds can randomly move away from their original locations, leaving a vacancy, or a hole. As the electron moves from one vacancy to another, the hole moves in exactly the opposite direction. Each broken bond generates electron-hole pairs, and the concentration of electrons equals the concentration of holes in an intrinsic semiconductor material. The concentration is called the intrinsic carrier concentration:

$$n_e = n_p = n_i \,. \tag{2.2}$$

From the above discussion, it is apparent that  $n_i$  is a function of temperature and the band gap, as shown in Fig. 2.3. At the same temperature, a material that has a smaller band gap tends to have a higher intrinsic carrier concentration. The intrinsic carrier concentration of a material increases when the temperatures increase. Because

Fig. 2.3. The relationship between the intrinsic carrier concentration  $(n_i)$ , temperature (T), and band gaps (E).

the lattice vibration is more rigorous at higher temperatures, the covalent bonds have a higher probability of breaking.

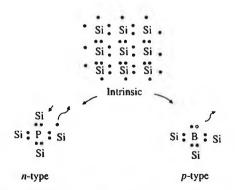

## 2.1.2. Doping of a semiconductor element

Doping is the process of adding foreign atoms to a semiconductor material. The foreign atoms are called dopants in the doping process. The most commonly used dopants are those elements in columns III and V of the periodic table. In a silicon crystal, each silicon atom has four valence electrons; it forms covalent bonds with its neighboring silicon atoms, as shown in Fig. 2.4. When the dopants are added into the crystal lattice, they take the place of silicon atoms at the crystal lattice site and are also covalently bonded to the neighboring silicon atoms. If the dopant has five valence electrons, such as P, As, or Sb, after forming the covalent bonding, there is one unbonded electron. This electron, when subjected to an external electrical field, becomes a charge carrier and conducts current. On the other hand, if the dopant happens to be Ga, B, or In, which have three valence electrons, it lacks one electron to form four covalent bonds with its neighboring silicon atoms. As a result, one vacancy (hole) is left, which can be easily filled by the neighboring moving electrons. In a

Fig. 2.4. A silicon atom forms covalent bonds with its neighboring silicon atoms. When doped with P, one electron is left unbounded; with B, one extra hole is formed.

silicon crystal, the motions of electrons and holes are equal and in opposite directions, and therefore the holes can be considered as positive charge carriers. Elements in column V of the periodic table are called n-type dopants or donors as they provide extra electrons when doped into silicon. On the other hand, elements in column III are called p-type dopants or acceptors when doped into silicon as they provide extra holes.

The extra electrons and holes resulting from the addition of dopants can be easily removed. At room temperature, the crystal lattice vibration energy is large enough to allow a complete ionization of these dopant atoms. In other words,

> $N_{\rm D}$  = donor-type dopant concentration = concentration of electrons = n,  $N_{\rm A}$  = acceptor-type dopant concentration = concentration of holes = p.

In both cases, n and p are much larger than  $n_i$ , which is the intrinsic carrier concentration. For complete ionization, all donor dopants become positive ions after they provide the extra electrons; the acceptor dopants become negative ions. Considering space charge neutrality,

$$q(p + N_{\rm D} - n - N_{\rm A}) = 0,$$

i.e.,  $p - n = N_{\rm A} - N_{\rm D}.$  (2.3)

From the analysis of quantum mechanics, it indicates that

$$np = n_i n_i . (2.4)$$

Therefore the following can be derived:

if

$$N_{\rm D} - N_{\rm A} \gg n_i$$

, then  $n = N_{\rm D} - N_{\rm A}$ . (2.5)

The corresponding hole concentration is

$$p = \frac{n_i^2}{N_{\rm D} - N_{\rm A}} \,. \tag{2.6}$$

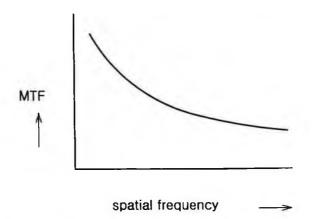

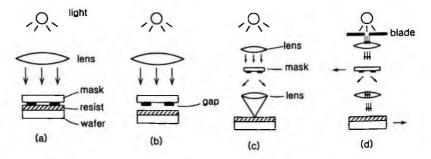

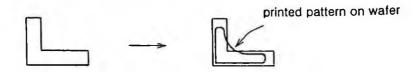

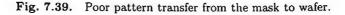

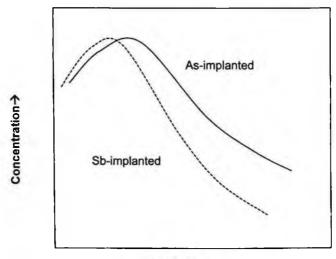

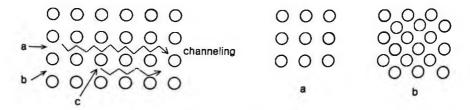

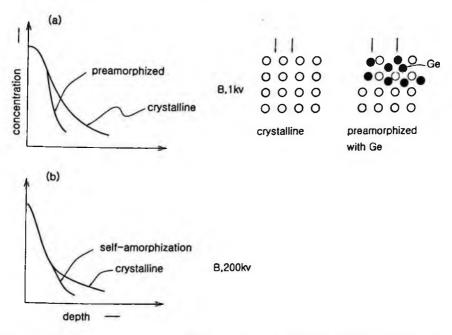

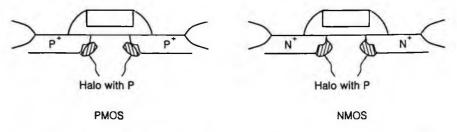

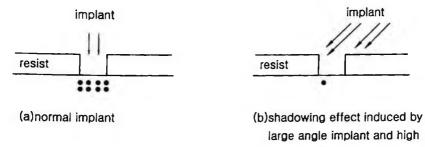

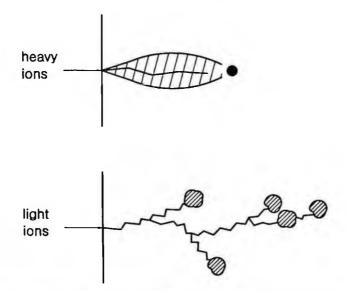

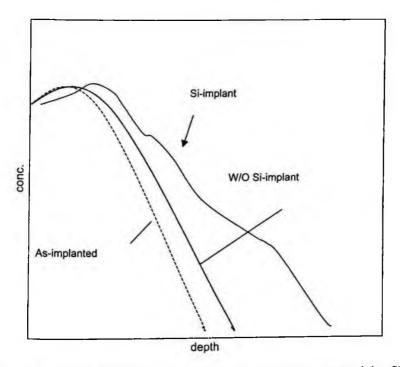

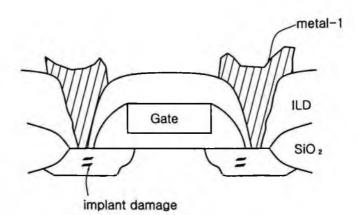

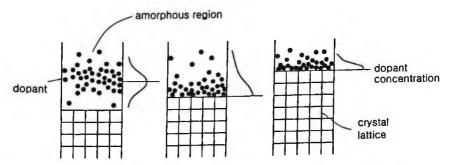

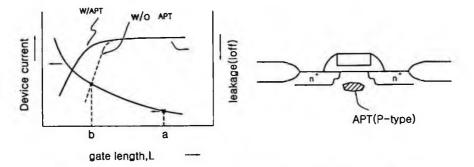

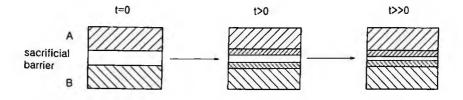

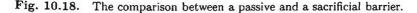

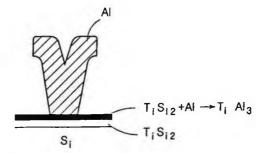

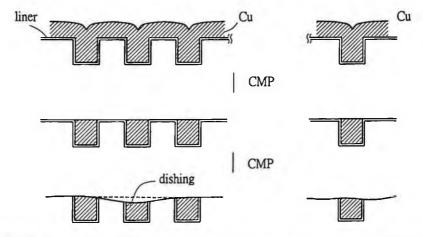

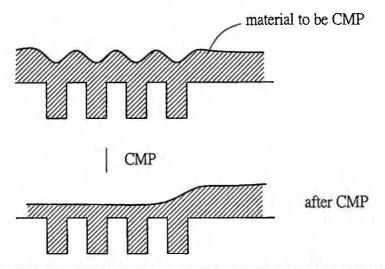

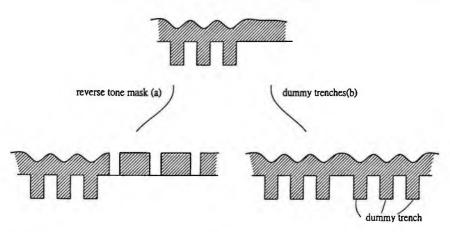

#### Example 2.1.